LPDDR5 Controller IP

Welcome to the ultimate LPDDR5 Controller IP hub! Explore our vast directory of LPDDR5 Controller IP

All offers in

LPDDR5 Controller IP

Filter

Compare

14

LPDDR5 Controller IP

from 6 vendors

(1

-

10)

-

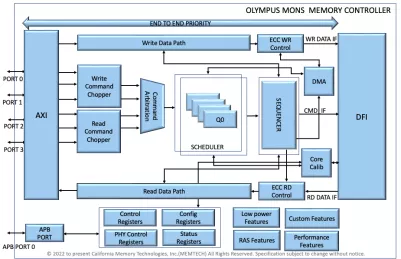

LPDDR5X DDR Memory Controller

- JEDEC LPDDR5X/LPDDR5 devices compatible

- Data rates up to 8533Mbps

- Multiple ARM AMBA AXI4/AHB/APB & Custom interfaces

-

DDR4/3, LPDDR5x/5/4x/4 Memory Controller IP

- Compliant with JEDEC standard for LPDDR5/4/3, DDR4/3

- DRAM rank of up to 4

- Lock-step-based controlling of multiple DRAM devices up to x64 DQ width

- Support for dynamic DRAM frequency scaling

-

LPDDR5X/5/4X/4 Memory Controller IP

- Intensive DRAM Utilization

- Ultra Low Power Consumption

- Extremely Low Latency

- Safety & Security

-

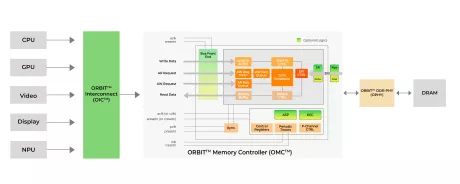

LPDDR Controller supporting LPDDR5X, LPDDR5, and LPDDR4X

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

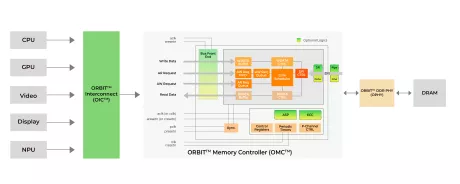

LPDDR Controller supporting LPDDR5X, LPDDR5 and LPDDR4X with Advanced Features Package

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR Controller ASIL B Compliant supporting LPDDR5X, LPDDR5 and LPDDR4X for Automotive Applications

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR Secure Controller supporting LPDDR5X, LPDDR5 and LPDDR4X with Advanced Features Package

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR5T / LPDDR5X / LPDDR5 Controller

- Support for all LPDDR5T/5X/5 devices

- Bank management logic monitors status of each bank

- Queue-based user interface with reordering scheduler

-

LPDDR Combo Controller - LPDDR4X/4 & LPDDR5T/5X/5

- Support for all LPDDR4 and LPDDR5 devices

- Bank management logic monitors status of each bank

-

DDR and LPDDR 5/4/3/2 controllers for low power and high Reliability, Availability and Serviceability (RAS)

- Four memory controller offerings: uMCTL2: multi-ported memory controller supporting JEDEC standard DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4, and LPDDR4X SDRAM and DIMM modules

- uPCTL2: Single-ported version of uMCTL2 with no internal scheduler; DDR5/4 controller: multi-ported memory controller supporting JEDEC standard DDR5, DDR4 SDRAMs and DIMM modules

- LPDDR5/4/4X controller: multi-ported memory controller supporting JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- High-bandwidth design with up to 64 CAM entries for Reads and 64 CAM entries for Writes, and latency as low as 6 clock cycles