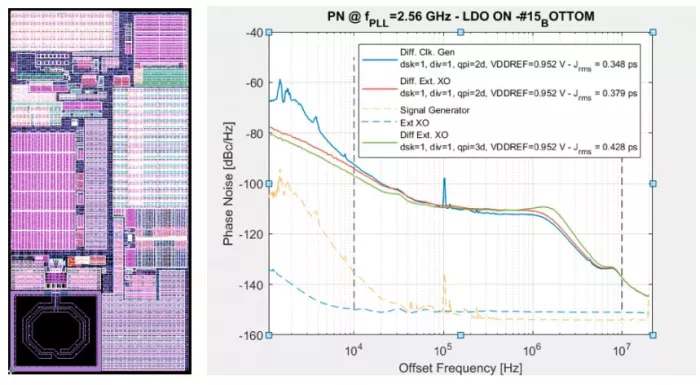

Fractional-N LC based frequency synthesizer with digital loop filter for RF LO synthesis or high performance clock generation applications.

Ultra-Low Phase Noise Digital LC PLL

Overview

Key Features

- Wideband integrated jitter <400fs in integer mode, <800fs in fractional mode with high-speed / clean reference with active fractional noise cancellation

- Passes PCIe6 reference clock requirements with wide margin

- Reference spur <200fs RMS

- Random period jitter <30fs RMS

- Low-leakage standby mode for fast re-locking

- “Instant” frequency lock from standby

- < 0.1% frequency error over PVT for open-loop DCO

- ±8% frequency tuning range

- Programmable loop bandwidth

- Low power (<10mW)

- Small (<0.1mm2)

Benefits

- Ultra-low phase noise allows PLL to be used for almost any high performance clocking application common in modern electronics

- Fully integrated so no external components are required

- Wide tuning range allows a single IP macro to be used for multiple applications

- Built-in frequency calibration enable high yield in mass production and ensures the frequency is always correct regardless of process or temperature variations

Block Diagram

Deliverables

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing module (.lib)

- LEF

- Application Note

Technical Specifications

Foundry, Node

TSMC 6FF, 7FF

Maturity

Silicon Proven

Availability

Available Now

TSMC

Pre-Silicon:

16nm

Silicon Proven: 6nm , 7nm

Silicon Proven: 6nm , 7nm

Related IPs

- Ultra-Low Phase Noise Delta Sigma Fractional-N LC PLL

- Ultra-Low Power Fractional-N digital PLL for IoT Applications in 40nm CMOS

- Low noise from 8GHz to 11.3GHz differential LC VCO

- Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- High Speed Low Jitter 16GHz Output LC PLL

- The True Random Number Generator (TRNG) Digital Noise Source