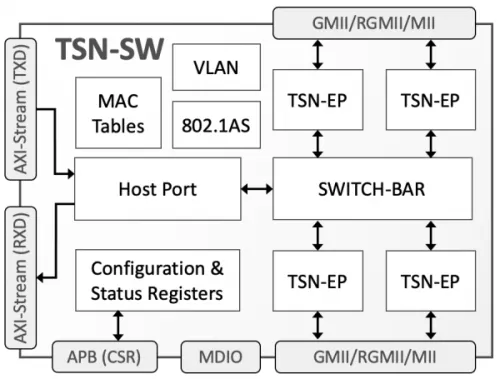

The TSN-SW implements a highly flexible, low-latency TSN Ethernet switch. It supports Ethernet bridging according to the IEEE 802.1Q-2018 standard and implements the essential TSN timing synchronization and traffic-shaping protocols,i.e.:

* IEEE 802.1as,

* 802.1Qav and 802.1Qbv,

* 802.1Qbu and 802.1br, and

* optionally the 802.1Qci and 802.1CB.

The quad-port, Layer-2 switch features cut-through switching at wire speed and can provide sub-microsecond port-to-port latency. The core is hence suitable for applications with demanding real-time requirements.

The TSN-SW operates efficiently under different usage scenarios and is highly configurable. Users can configure key factors via the core’s control registers:

the mapping of VLAN priority levels to TSN traffic classes,

the traffic scheduling and preemption parameters,

the treatment of special frames (i.e., broadcast, unknown, & internal), as well as

the VLAN ID and MAC lookup tables used for frame forwarding and filtering.

The host system can also switch the mode of operation of each individual port from cut-through to store-and-forward to eliminate the propagation of bad frames at the cost of increased latency. The core otherwise operates autonomously and only requires software assistance at runtime for correct time synchronization; a light-weight ptp/802.1AS software stack comes with the core for that purpose.

The TSN-SW uses standard AMBA® interfaces to ease integration. Its control and status registers are accessible via a 32-bit-wide APB bus, and packet data can be exchanged with the host system via AXI-Streaming interfaces with 32-bit data buses.

The TSN-SW is designed with industry best practices and is available in synthesizable RTL (Verilog 2001) source code or as a targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample synthesis and simulation scripts, an extensive testbench, and comprehensive documentation.

TSN Ethernet Switch

Overview

Key Features

- Low-Latency & Flexible Ethernet Switch

- Four full-duplex Ethernet ports plus one internal port

- Layer-2, cut-through switching at wire speed

- Store-and-forward mode can also be enabled per port at run time

- Sub-microsecond port-to-port latency, in cut-through mode 10/100/1000 Mbps Ethernet speeds (2.5/10+ Gbps on request)

- 802.1Q-2018 Tagged VLAN support

- Port-based VLAN

- Configurable VLAN-PCP to TSN-queue mapping (QoS by PCP)

- Flexible VLAN and MAC forwarding & filtering

- Configurable VLAN-ID & MAC lookup table for dynamic and static entries

- Automatic aging table

- TSN Features

- Ready for IEEE 802.1as (lightweight software stack available)

- Traffic shaping per IEEE 802.1Qav & IEEE 802.1Qbv with eight TSN-Queues

- Frame preemption per IEEE 802.1Qbu and IEEE 802.3br

- Frame Replication and Elimination for Redundancy per IEEE 802.1Qci and Per-Stream Filtering and Policing (PSFP) per IEEE 802.1CB (coming soon)

- Easy System Integration

- AMBA™/AXI4 SoC Interfaces

- 32-bit APB control/status interface

- 32-bit AXI4-Stream for packet data

- MII, GMII or RGMII, and MDIO Ethernet PHY interface per port

- Requires minimal host assistance for initialization and operation

- Provides a wide range of statistics via optionally instantiated counters

- Complete reference designs available for Altera and Xilinx, including lightweight PTP stack sample application software

Block Diagram

Deliverables

- Verilog RTL source code or targeted FFGA netlist

- Testbenches

- Sample Simulation and Synthesis scripts

- Comprehensive Documentation

- Lightweight PTP stack.

Technical Specifications

Maturity

Silicon Proven

Availability

Now