Implements a communication controller that transmits and receives complete Local Interconnect Network (LIN) frames to perform serial communication according to the LIN Protocol Specification.

The LIN controller can be implemented as a master or as a slave and operate on LIN 1.3, 2.0, 2.1 or 2.2 LIN network. It uses a single master/multiple slave concept for message transfer between nodes of the LIN network. The message transfer can be controlled via a microcontroller interface and a LIN transceiver is needed for the connection to the LIN bus.

The LIN-CTRL is used to interface sensors and actuators in a variety of applications such as automotive, industrial, and home appliances.

The core is a microcode-free design developed for reuse in ASIC and FPGA implementations. The scan-ready design is strictly synchronous with positive-edge clocking and no internal tri-states. The robustly verified core has been production-proven multiple times.

The LIN-CTRL core is available in two versions: Standard, and Safety-Enhanced. The Safety-Enhanced version implements ECC for SRAMs protection and uses spatial redundancy for protecting the inner logic of the core. The Safety-Enhanced versions are certified as ISO-26262 ASIL-D Ready. More ISO-26262

LIN Bus Master/Slave Controller Core

Overview

Key Features

- Support of LIN specifications 2.0, 2.1, and 2.2A

- Backward compatible with LIN specification 1.3

- Configurable for support of master or slave functionality

- Programmable data rate between 1 Kbit/s and 20 Kbit/s (for master)

- Automatic bit-rate detection (for slave)

- 8-byte data buffer

- Generic 8-bit microcontroller interface

- Wrappers converting the generic microcontroller interface to AMBA APB or AHB are offered with the core

- Slave can be implemented with or without clock synchronization

- Fully synchronous design, available in VHDL or Verilog, completely synthesizable

- Optional safety-enhanced version certified as ISO-26262 ASIL-D Ready

- The LIN Controller synthesizes to approximate 2500 to 3800 gates depending on the configuration

- Robustly verified and multiple times production-proven IP core

- LIN Verification IP is available to use with this core

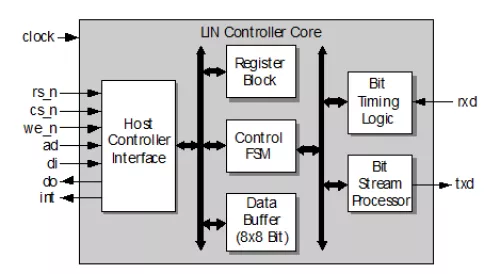

Block Diagram

Applications

- The LIN core can be utilized for a variety of applications including;

- low cost automotive networks

- interfaces for sensors and actuators

Deliverables

- HDL RTL source code (ASICs) or post-synthesis EDIF netlist (FPGAs)

- Testbench

- Sample driver in C code

- Simulation script, vectors, expected results

- Synthesis script (ASICs) or place and route script (FPGAs)

- Comprehensive user documentation, including detailed specifications and a system integration guide

Technical Specifications

Maturity

Production Proven

Availability

Now