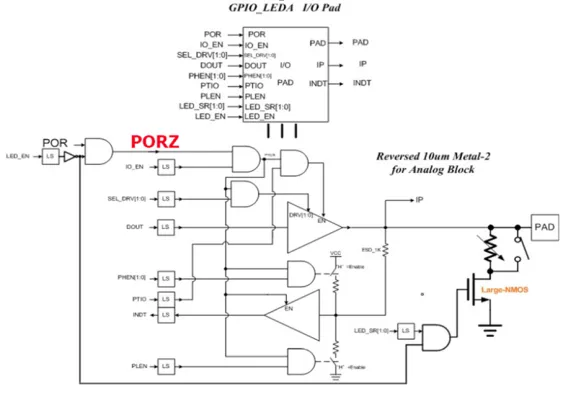

GPIO_LED I/O

Overview

U40LPGPIOLEDV1 is a general purpose I/O with LED driving IP. It is based on UMC 40nm low power process.

Key Features

- Process: UMC 40nm Logic and Mixed-Mode 2.5V/1.1V Low Power Process

- Pill-up resistor: disable/2.2K/50K

- Driving: 4mA/8mA/16mA/32mA

- Pull-low enable

- Output enable

- IO enable

- LED resistor 0/200/300/500

- Power Supply: IO power supply 3.3V, Core power supply 1.1V, Operated Ambient Temperature: Ta = -40 ~ 85°C

- Area < 90um x 120um

Block Diagram

Technical Specifications

Foundry, Node

UMC 40nm Logic and Mixed-Mode 2.5V/1.1V Low Power Process

Maturity

Available on request

Availability

Available

Related IPs

- IO & ESD solutions supporting GPIO, I2C,RGMII, SD, LVDS, HDMI & analog/RF across multiple technology nodes

- DDR2/DDR3/DDR3L/LPDDR/LPDDR2/LPDDR3 6 in one combo IO with auto calibration - 40nm LL

- 28nm Wirebond IO library with dynamically switchable 1.8V/ 3.3V GPIO, 5V I2C open-drain, 1.8V & 3.3V analog, OTP program cell, and HDMI & LVDS protection macros - featured across a variety of metal stack and pad configuration options

- RGMII I/O offerings

- 1.8V Power Support I/O Pad Set

- 1.8V Programmable 100MHz Oscillator I/O Pad Set