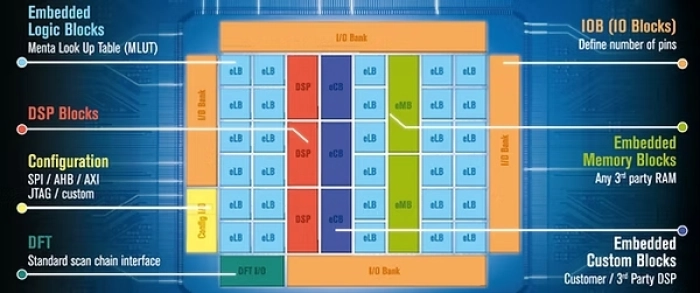

These eFPGAs are high-density embedded programmable logic IPs for use in SoCs or ASICs. They are designed to address various markets and applications. The eFPGA IP cores empower designers to define the specific resources required for their applications needs.

Available as Soft RTL or Hard GDSII IP.

Menta is committed to maximizing process portability, so our eFPGAs have been silicon-proven on more technology nodes than any other eFPGA vendor. Menta supports any CMOS foundry and node from 350nm to 5nm or less. To date, Menta eFPGAs have been successfully manufactured on technologies as diverse as: STM130, STM65, TSMC 28HPC+, TSMC 12FFC and GLOBALFOUNDRIES 12LP. Menta eFPGAs are qualified on GLOBALFOUNDRIES® 32 SOI and 14LPP. Menta is also a 22 FDXcelerator Partner. Menta IPs are currently being delivered on XFAB 180nm, STM28 FDSOI and others.

Foundry, Node

Any CMOS process

Maturity

Delivered on 10+ processes at 4 foundries

Availability

Today

GLOBALFOUNDRIES

In Production:

14nm

LPP

Pre-Silicon:

12nm

,

14nm

,

14nm

LPE

,

14nm

LPP

,

20nm

LPM

,

22nm

,

22nm

FDX

,

28nm

,

28nm

FDSOI

,

28nm

HPP

,

28nm

LPH

,

28nm

SLP

,

32nm

,

40nm

LP

,

55nm

,

55nm

LPX

,

65nm

,

65nm

LP

,

65nm

LPe

,

90nm

,

90nm

LP

,

130nm

,

130nm

HP

,

130nm

LP

,

130nm

LV

,

180nm

,

180nm

LL

,

180nm

LL

,

180nm

LP

,

180nm

LP

,

250nm

,

250nm

LPE

,

350nm

Silicon Proven:

14nm

LPP

,

32nm

LFoundry

Pre-Silicon:

150nm

,

350nm

Renesas

Pre-Silicon:

40nm

,

55nm

,

90nm

,

150nm

SMIC

Pre-Silicon:

14nm

,

28nm

,

28nm

HK

,

28nm

HKC+

,

28nm

PS

,

40nm

LL

,

55nm

G

,

55nm

LL

,

65nm

LL

,

90nm

G

,

90nm

LL

,

110nm

G

,

130nm

EEPROM

,

130nm

G

,

130nm

LL

,

130nm

LV

,

150nm

G

,

150nm

LV

,

160nm

G

,

160nm

LL

,

180nm

EEPROM

,

180nm

G

,

180nm

LL

,

250nm

G

Samsung

Pre-Silicon:

7nm

,

8nm

,

10nm

,

14nm

,

28nm

FDS

,

28nm

LPH

,

28nm

LPP

,

32nm

LP

,

45nm

LP

,

65nm

LP

,

90nm

LP

Silterra

Pre-Silicon:

90nm

,

130nm

,

180nm

TSMC

Pre-Silicon:

7nm

,

12nm

,

16nm

,

28nm

HPM

Silicon Proven:

28nm

HPCP

Tower

Pre-Silicon:

130nm

,

180nm

,

180nm

,

180nm

,

500nm

UMC

Pre-Silicon:

14nm

,

28nm

,

28nm

HLP

,

28nm

HPC

,

28nm

HPM

,

28nm

LP

,

40nm

,

40nm

LP

,

55nm

,

65nm

LL

,

65nm

LP

,

65nm

SP

,

80nm

,

90nm

G

,

90nm

LL

,

90nm

SP

,

110nm

,

130nm

,

150nm

,

162nm

,

180nm

,

250nm

,

350nm