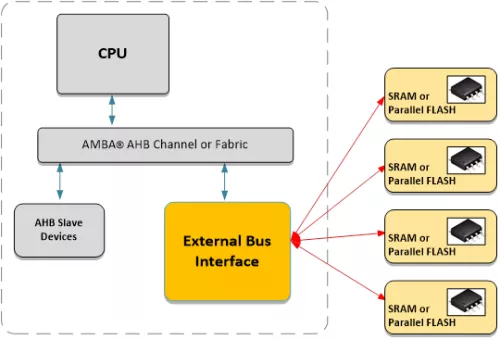

The AHB External Bus Interface (EBI) allows a CPU or AHB Master (such as a DMA core) to transmit and receive data to an external device such as an external SRAM or Parallel Flash device.

The number of read wait states, the number of write wait states, and the memory width are all configurable through the APB register interface of the EBI. The EBI allows word, half-word, and byte width addressing to 32-bit, 16-bit, and 8-bit external devices.

The EBI translates AHB writes and reads into writes and reads for the external device. In order to accomplish this task, the EBI is comprised of five major functional blocks: APB Register Interface, Wait State Generation, Address Generation, Control Signal Generation, and Data Steering.

AHB External Bus Interface

Overview

Key Features

- Interfaces AHB bus to external SRAM or Parallel Flash devices

- Scalable number of external devices

- Programmable access times

- Independent 8, 16, or 32-bit data interface

- Programmable wait states per device interface

- Selects up to 4 external devices

- Byte, 16-bit half-word and 32-bit word accessible

- Single cycle external bus access selectable

- Single cycle processor bus access

Block Diagram

Technical Specifications

Maturity

Silicon Proven

Availability

Now