LPDDR4 PHY IP

Welcome to the ultimate LPDDR4 PHY IP hub! Explore our vast directory of LPDDR4 PHY IP

All offers in

LPDDR4 PHY IP

Filter

Compare

59

LPDDR4 PHY IP

from 10 vendors

(1

-

10)

-

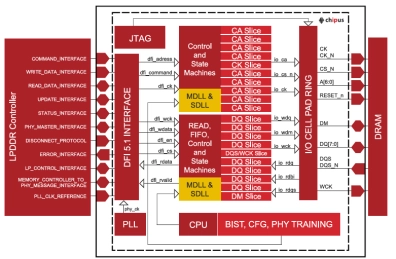

LPDDR4/4x/5/5x PHY

- Supports JEDEC SDRAM standards including LPDDR4 (1.1V), LPDDR4x (0.6V), LPDDR5/5x (0.5V)

- Supports data rates up to 4,266 Mbps LPDDR4/LPDDR5 and up to 8,533 Mbps LPDDR5x

- Support for 16, 32 and 64-bit operation

-

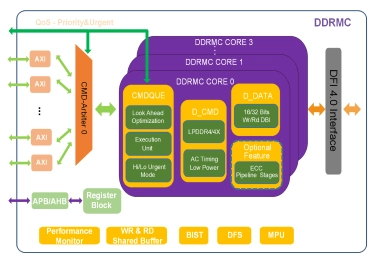

LPDDR4/4x IP solution

- Compatible with LPDDR4/4x up to 3733Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

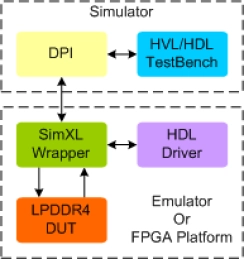

LPDDR4 Synthesizable Transactor

- Supports 100% of LPDDR4 protocol standard JESD209-4,JESD209-4A,JESD209-4B,JESD209-4C,JESD209-4D,JESD209-4X and JESD209-4Y (proposed)

- Supports all the LPDDR4 commands as per the specs

- Supports memory densities upto 32GB

- Supports device types X8 and X16

-

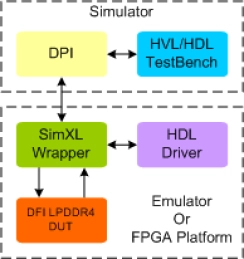

LPDDR4 DFI Synthesizable Transactor

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports LPDDR4 devices compliant with JEDEC LPDDR4 SDRAM Standard JESD209-4, JESD209-4A, JESD209-4B, JESD209-4C (Proposed), JESD209-4X and LPDDR4Y (Proposed).

- Supports for Read data-eye training

- Supports for Read gate training

-

LPDDR4X PHY

- Compatible with LPDDR4X, with a maximum rate up to 4267Mbps

- Compliant with DFI 4.0 for PHY and control interfaces

- Flexible channel architecture

- Supports PHY-independent training mode using an embedded processor

-

LPDDR4 multiPHY V2 - UMC 28HPC+18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4 multiPHY V2 - TSMC28HPC+18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC16FFC18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4 multiPHY V2 - TSMC16FFC18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC12FFC18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor