MIPI D-PHY IP for UMC

Welcome to the ultimate MIPI D-PHY IP for UMC hub! Explore our vast directory of MIPI D-PHY IP for UMC

All offers in

MIPI D-PHY IP

for UMC

Filter

Compare

38

MIPI D-PHY IP

for UMC

from 7 vendors

(1

-

10)

-

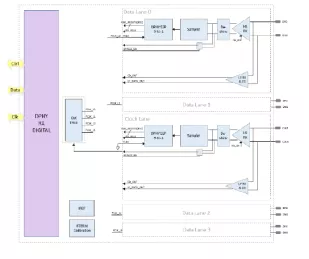

MIPI D-PHY Universal IP in UMC 28HPC+

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

- Embedded, high performance, and highly programmable PLL

- Supports both low-power mode and high speed mode with integrated SERDES

-

MIPI DPHY v1.2 TX 4 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY v1.2 RX 4 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Tx 2 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Rx 2 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Tx 4 Lanes - UMC 22ULP 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Rx 4 Lanes - UMC 22ULP 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

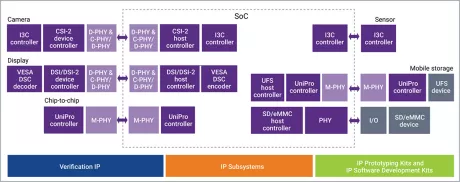

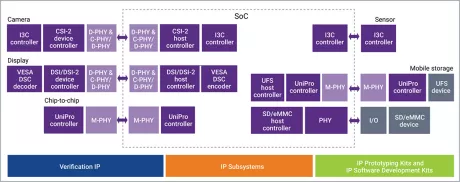

MIPI DPHY_RX v1.2, 2C4D, UMC 28HPC+, E/W orientation

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

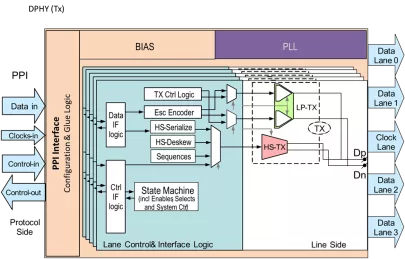

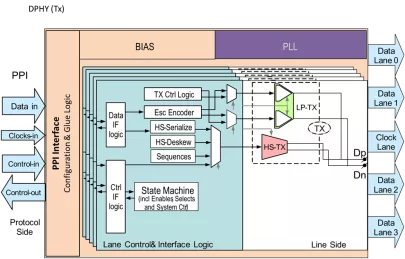

MIPI DPHY_TX v1.2, 1C4D, UMC 28HPC+, E/W orientation

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

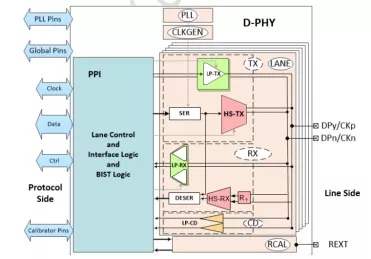

MIPI D-PHY Rx IP, Silicon Proven in UMC 55LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s