HDMI PHY IP for UMC

Welcome to the ultimate HDMI PHY IP for UMC hub! Explore our vast directory of HDMI PHY IP for UMC

All offers in

HDMI PHY IP

for UMC

Filter

Compare

14

HDMI PHY IP

for UMC

from 5 vendors

(1

-

10)

-

HDMI 2.0 TX PHY 6Gbps in UMC 28HPC 1.8V, North/South Poly Orientation

- Support for key HDMI 2.0 features such as 4Kx2K resolution at 60 Hz frame rate, YCbCr 4:2:0 pixel encoding format, TMDS scrambling, High Dynamic Range (HDR), CEC 2.0, and 18.0 Gbps aggregate bandwidth

- Compliant with HDMI 2.0 and HDCP 2.3, 1.2 specification

- Optimized for low power and small area

- Timing hardened blocks enable simplified placement and design closure

-

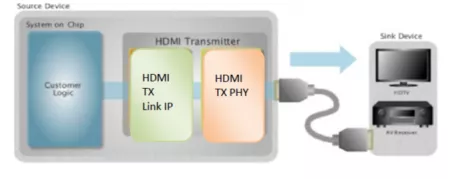

HDMI 1.4 Tx PHY & Controller IP, Silicon Proven in UMC 65/55ULP

- HDMI version 1.4 compliant transmitter

- Supports DTV from 480i to 1080i/p HD resolution

- Supports 24bit, 30bit and 36bit color depth per pixel

- Integrated cable terminator

-

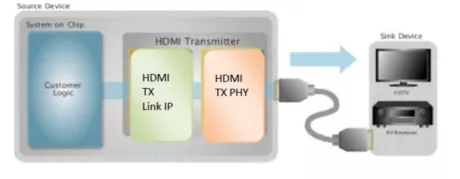

HDMI 1.4 Tx PHY & Controller IP, Silicon Proven in UMC 40SP

- HDMI version 1.4 compliant transmitter

- Supports DTV from 480i to 1080i/p HD resolution

- Supports 24bit, 30bit and 36bit color depth per pixel

- Integrated cable terminator

-

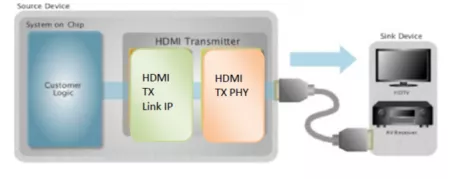

HDMI 1.4 Tx PHY & Controller IP, Silicon Proven in UMC 28HPC

- HDMI version 1.4 compliant transmitter

- Supports DTV from 480i to 1080i/p HD resolution

- Supports 24bit, 30bit and 36bit color depth per pixel

- Integrated cable terminator

-

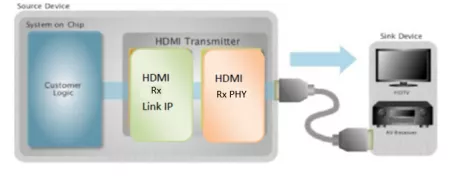

HDMI 1.4 Rx PHY & Controller IP, Silicon Proven in UMC 65/55ULP

- HDMI version 1.4 compliant receiver

- Supports DTV from 480i to 1080i/p HD resolution

- Supports 24bit, 30bit and 36bit color depth per pixel

- HDMI version 1.4a, HDCP revision 1.3 and DVI version 1.0 compliant receiver

-

HDMI 2.0 Tx PHY & Controller IP, Silicon Proven in UMC 28HPC

- HDMI version 2.0b compliant transmitter

- Supports CEA-861F/VESA DMT up to 4K2K resolution@60fps

- Supports 3D formats (Frame packing/Side by Side Half/Top & Bottom)

- Wide range channel speed up to 6.0Gbps

-

HDMI 2.0 Rx PHY & Controller IP, Silicon Proven in TSMC 40LP

- HDMI version 2.0b compliant receive.

- Supports HDCP 2.2/HDCP 1.4.

- Supports CEA-861F/VESA DMT up to 4K2K.

- Supports 3D formats (Frame packing/Side by Side Half/Top & Bottom).

-

HDMI2.0 TX PHY

- Area: 0.604mm2 (592um x 1020um) including IO and ESD

- Note: The area parameters are for reference only. Please refer to the final LEF file for the actual values.

- Compliant with HDMI2.0, HDMI1.4 and DVI1.0 specifications

- Up to 6Gbps per data channel

-

HDMI2.0/1.4 TX PHY & Controller

- Compliant with HDMI2.0, HDMI1.4 and DVI1.0 specifications

- Up to 6Gbps per data channel

- Typical 24MHz or 27MHz reference clock

- Supports YUV4:4:4, YUV4:2:2, YUV4:2:0 and RGB4:4:4 video formats

-

HDMI2.0 Receiver PHY & Controller

- Area: 0.92mm2 including IO and ESD for PHY and 0.78mm2 for Controller without memory

- Compliant with HDMI2.0, HDMI1.4 and DVI1.0 specification

- Typical 24Mhz reference clock

- Support YUV4:4:4, YUV4:2:2, YUV4:2:0 and RGB4:4:4 video format