The Ultra-Low Latency 1G Ethernet MAC and PCS is the industry leading solution for latency critical Ethernet applications. The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances.

It includes a rich set of standard and advanced features making it ideal for a large number of applications. The IP core can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic, up to jumbo frame size, with no dropped packets.

Ultra-Low Latency 1G Ethernet MAC and PCS

Overview

Key Features

- MAC FEATURES

- Deficit idle counter (DIC) to maintain a 12-byte inter-packet gap (IPG) average

- Programmable IPG length (down to 1-byte)

- Programmable Maximum Receive Unit (MRU), Maximum Transmission Unit

- User facing logic interface 16-bit @ 250MHz

- Ethernet flow control and congestion management using pause frames with programmable quanta

- Programmable Tx minimum packet length with enable/disable padding option

- Programmable Rx minimum packet length

- Tx Frame Check Sequence (FCS) computation and insertion

- Programmable Tx FCS pass-through and corruption insertion modes

- Programmable keep/strip Rx FCS

- Programmable Rx FCS error detection and marking

- Programmable Tx and Rx path VLAN detection (Programmable TPID, stacked VLAN)

- Configurable statistics vector and collector on transmit and receive MAC data

- PCS FEATURES

- Supports 1000BASE-X PHY based on 8B/10B encoding

- Running disparity compute

- Configurable statistics vector and collector on transmit and receive PCS

Benefits

- Compliant with the IEEE 802.3-2012 High Speed Ethernet Standard

- Ethernet MAC supports 1GbE line rate with flexible feature set

- Soft PCS logic interfacing to standard serial transceiver at 1.25Gbps

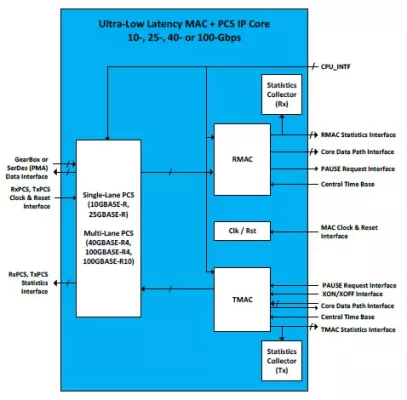

Block Diagram

Applications

- High Frequency Trading

- Smart NIC

- Low-Latency Switches

- Low-Latency Radio

- Test and Monitoring Equipment

Deliverables

- Datasheet & user guide

- Encrypted Verilog

- Constraints file

- Reference design

- Technical support

- Optional IP design customization

Technical Specifications

Related IPs

- 10-Gbps Ultra-Low Latency Ethernet MAC and PCS

- Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- 1G UDP Offload+MAC+PCIe+Host_IF Ultra-Low Latency (SUOE+PCIe)

- 1G TCP Offload Engine TOE+MAC+Host_IF Ultra-Low Latency (STOE)

- 1G TCP Offload Engine TOE+MAC+PCIe+Host_IF Ultra-Low Latency (STOE+PCIe)

- 25G Ultra Low latency, 64-bit Ethernet MAC + PCS Solution (64-bit and 128-bit UI)