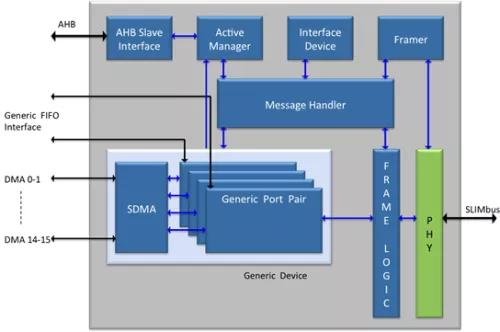

The MIPI SLIMbus Host typically resides in a mobile platform’s application processor and provides two-wire, multi-drop connectivity with multiple audio and other low/mid bandwidth peripheral devices. The Arasan SLIMbus Host Controller IP is designed to provide MIPI SLIMbus 1.01 compliant connectivity to a SoC.

As a SLIMbus host, this IP is responsible for the establishment, maintenance and shutdown of the entire SLIMbus system under control of the host software drivers/stack and in response to the presence and bandwidth requirements of the various SLIMbus devices on the bus.

SLIMbus has a TDM channel allocation structure for control messages and data. When its Framer is active, the host drives the SLIMbus clock, creates the SLIMbus frames, and enables the various devices to synchronize and share the available bandwidth.

This IP contains a configurable generic device that transfers data to and from remote SLIMbus components and the SOC’s system memory. Alternately, one or more port pairs of the generic device can be used by SLIMbus host component to incorporate bridge functions to legacy interfaces, like I2S, I2C and SPI, or interface directly to audio DAC’s and ADC’s.

MIPI SLIMbus Host Controller v2.0

Overview

Key Features

- Compliant with MIPI SLIMbus Specification version 2.0

- Delivered in Reuse Methodology Manual (RMM) compliant Verilog RTL format

- Small footprint

- Contains full-featured active manager and interface devices, with support for

- Dynamic channel allocation and management

- All SLIMbus Core Messages

- Error handling and recovery, as defined in the MIPI SLIMbus specification

- Embedded framer which can be active or passive, and supports SLIMbus clock generation handoff to/from framers in other components, with support for

- Clock Gears 1 to 10, either as clock source or clock receiver

- Maximum of 28.8 MHz bit-serial rate

- Dynamic SLIMbus clock frequency scaling and clock pause/resume minimizes power

- Contains one generic device with up to 8 active port pairs; each port supports

- Isochronous, Pushed, Pulled, Asynchronous Simplex, Extended Asynchronous Simplex and Locked transport protocols over SLIMbus with data segment size of 1 to 31 slots

- Interface options for applications processor

- Generic FIFO Interface

- Audio or peripheral data sample sizes of 8, 16, 24 or 32 bits

- Different port pairs can have different sampling rates

- Slave DMA Interface

- Each generic port has separate channel to external DMA master

- Interrupt wakeup mechanism to turn system bus interface on when SLIMbus host ready to source/sink system memory data

- 32 bit AHB 2.0 Slave Interface to CPU/Memory sub-system

- System Clock frequency range from 66 to 150 MHz

- Used by driver to configure the IP using Programmed IO

- Optionally used for data transfer to/from generic device

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers

- Verilog HDL of the IP Core

- Synthesis scripts

- Verification environment

- User guides for design and verification

Benefits

Block Diagram

Deliverables

Technical Specifications

Maturity

In Production

Availability

Now