The AMBA ATB Verification IP provides an effective & efficient way to verify the components interfacing with the AMBA ATB interface of an IP or SoC. The AMBA ATB VIP is fully compliant with standard AMBA 5 ATB (aka ATB-C), AMBA 4 ATB (aka ATB v1.1), and AMBA 3 ATB (aka ATB v1.0) protocol. This VIP is a light weight VIP with an easy plug-and-play interface so that there is no hit on the design cycle time.

AMBA ATB Verification IP

Overview

Key Features

- Compliant to AMBA 5 ATB (aka ATB-C), AMBA 4 ATB (aka ATB v1.1) and AMBA 3 ATB (aka ATB v1.0) Protocol.

- Parameterized address and data width and hence capable of configuring all possible ATB and TPIU bus widths.

- Bus Monitor is easy to Plug-in and is compliant with standard specifications.

- Support for static and dynamic protocol checks.

- Supports Flow control using ATVALID and ATREADY signaling to track the data.

- Supports unique ATID to differentiate between traces from different sources.

- Supports Buffer flush feature and enables and disables access for the clock.

- Supports FIFO memory to store the trace data item generated.

- Supports Synchronization request to insert synchronization information in the trace stream.

- Supports Wake-up signal to indicate any activity associated with an ATB interface.

- Capable of performing register value checks for register bank modified by APB interface.

- Supports masking of any specific error.

- Provides a full bus coverage analysis.

- Supports multi-master mode

- Supports valid data capture functionality

- Supports a variety of error injection modes.

- TPIU slave supports all Flushing modes:

- Manual Flush, Flushing, Trigin

- TPIU slave supports all three modes:

- Normal, Continuous (Formatter supported), and Bypass

- Support for all patterns and modes of Pattern Generator.

- Support for TPIU Lite is also available.

- Supports transaction logging with a detailed description of each transfer.

- Support GUI analyzer for easy debugging

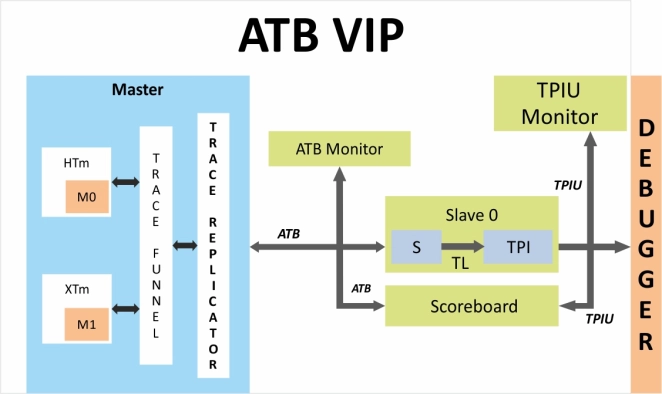

Block Diagram

Technical Specifications

Related IPs

- SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- SPI Controller IP- Master-only, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- SPI XIP Flash Memory Controller IP – Programmable IO & Execute-In-Place (XIP) via second AMBA Interface

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect

- AMBA ATB Assertion IP