The AMBA® 4 ACE™ Verification IP provides an effective & efficient way to verify the components interfacing with ACE interface of an IP or SoC. The AMBA® 4 ACE™ VIP is fully compliant with ACE specifications from ARM IHI 0022E ID022613. This is a light weight VIP with easy plugand-play interface so that there is no hit on the design cycle time.

AMBA 4 ACE Verification IP

Overview

Key Features

- Fully compliant to the AMBA® 4 ACE™ Specification.

- Support for all type of AMBA 4 ACE devices.

- Rich set of configuration parameters to control ACE functionality.

- Parametrized bus width and cache line size.

- Interconnect model ensures that the interaction between all bus components is correct and follows the ACE protocol.

- Response comparison for all response channels.

- Supports optional Snoop Data channel.

- Supports Cache Maintenance transactions.

- Support to configure read/write transaction priority to the same address, issued at the same time.

- Capability of interconnect to modify a transaction.

- Supports sequencing of transactions for transactions occurring at approximately the same time to the same cache line.

- Support for Barrier transactions.

- Configurable modes for Valid and Ready signals on different channels.

- Support for Speculative read.

- Comprehensive Test Suites support constrained randomization and error injection.

- Supports advanced System Verilog features like constrained random testing.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using protocol check functions, static and dynamic assertion.

- Built in Extensive Coverage Across the Channels.

- Provides a comprehensive user API (callbacks) for each component to override actual behaviour of component e.g. overriding write data from Master.

- Graphical analyser to show transactions for easy debugging.

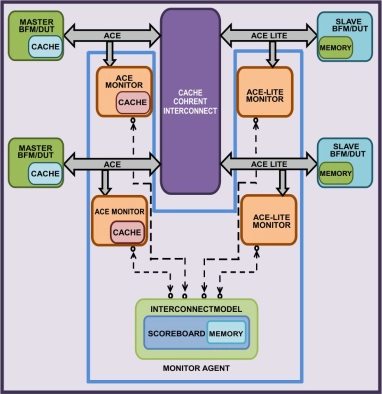

Block Diagram

Technical Specifications

Related IPs

- AMBA 4 ACE Verification IP

- SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- SPI Controller IP- Master-only, Parameterized FIFO, AMBA APB / AHB / AXI Bus

- SPI XIP Flash Memory Controller IP – Programmable IO & Execute-In-Place (XIP) via second AMBA Interface

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect