SD Controller IP

Welcome to the ultimate SD Controller IP hub! Explore our vast directory of SD Controller IP

All offers in

SD Controller IP

Filter

Compare

32

SD Controller IP

from 14 vendors

(1

-

10)

-

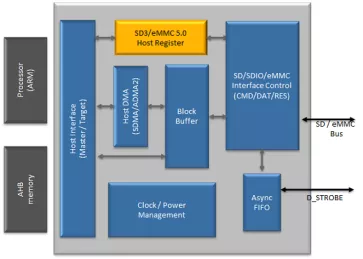

SD 3.0 / SDIO 3.0 / eMMC 5.0 Host Controller

- Memory Card / Form Factors:

- IP Details:

-

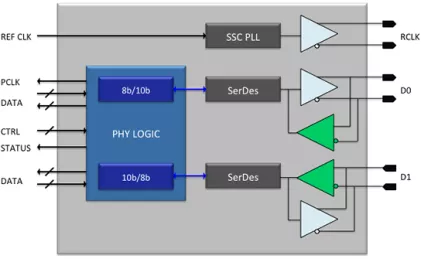

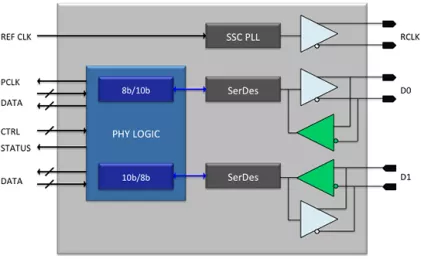

SD 4.0 UHS-II PHY TSMC 28nm HPM North-South

- Compliant with SD Specifications Part 1 UHS-II Addendum v1

- Supports data rate between 390 Mbps to 1.56 Gbps per lane

- Supports peak interface speed of 3.12 Gbps in Half-duplex mode; 1.56 Gbps in Full-duplex mode

- Sub-LVDS differential PHY signaling

-

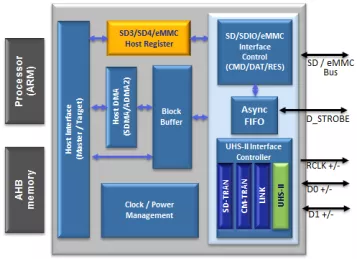

SD 4.1 SDIO 4.1 Host Controller IP

- SD4.0

- SDIO4.0

- eMMC5.0

-

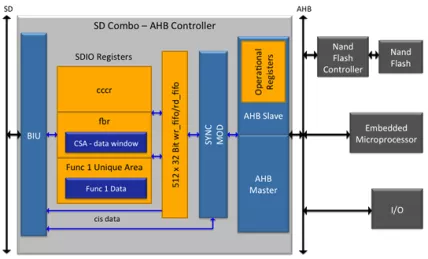

SD 3.0 / SDIO 3.0 Combo Device Controller

- Meets SD Memory Card Physical Layer Specification version 3.0

- Meets SDIO card specification ver 3.0

- Host clock rate variable between 0 and 208 MHz

- All SD bus modes supported including SPI, 1 and 4 bit SD.

-

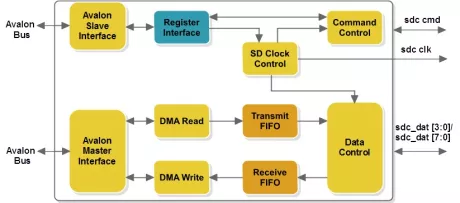

SD/eMMC Host Controller

- Supports selection between SD and eMMC

- Supports CRC7 and CRC16 generation and verification on Hardware

- Supports multiple block transfer

-

SD 4.0 UHS-II PHY in TSMC 40LP

- Compliant to SD Specifications Part 1 UHS-II Specification Volume 2: PHY* and SD Specifications Part 1 UHS II

- Specification Volume 1: System and Protocol”

- Per lane data rate between 390Mb/s to 1.56Gb/s

- Supports peak interface speed of 3.12Gb/s (Half-duplex); 1.56Gb/s in Full-duplex mode

-

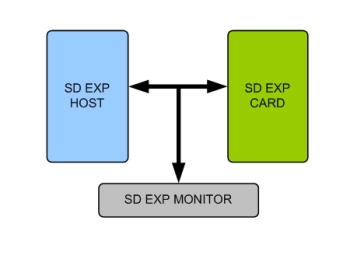

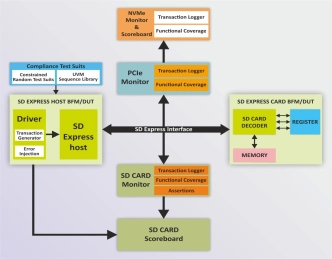

SD Express Verification IP

- Supports SD specification version 7.0, 7.10 and 8.0(Draft) compliant

- SD Express card supports NVMe protocol (revision 1.3, 1.3a, 1.3b, 1.3c, 1.3d and 1.4) over PCIe Interface

- Supports PCI-Express (PCIe) dual simplex point to point serial connection

- Bus Speed Mode - using PCIe Differential Interface lines

-

SD Express Card Verification IP

- Compliant to SD Specification v7.00

- SD Express card supports NVMe protocol over PCIe Interface

- Supports SD and PCIe Mode

- Supports PCIe Gen3 Single lane with Dual simplex point to point serial connection

-

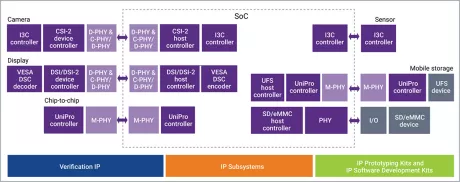

SD/eMMC Lite Host Controller IP

- Compliant with the SD 6.0, SDIO 4.10 and eMMC 5.1 specifications and earlier versions

- Supports advanced eMMC features including HS400 mode and built-in CQE with priority sensitive scheduling algorithm for high performance

- Low power features with power gating and multi-power rails

- Supports the host controller interface (HCI) specification for SD ensuring the usability of standard software drivers with support for SDMA, ADMA2 and ADMA3 modes

-

SD/eMMC Host Controller IP

- Compliant with the SD 6.0, SDIO 4.10 and eMMC 5.1 specifications and earlier versions

- Supports advanced eMMC features including HS400 mode and built-in CQE with priority sensitive scheduling algorithm for high performance

- Low power features with power gating and multi-power rails

- Supports the host controller interface (HCI) specification for SD ensuring the usability of standard software drivers with support for SDMA, ADMA2 and ADMA3 modes