CoreABC is a simple, low gate count controller for Advanced Microcontroller Bus Architecture (AMBA®) advanced peripheral bus (APB) based designs. In particular, it is targeted to control CoreAI and CorePWM in mixed-signal applications, but it can be used to control any APB or APB3 bus IP core. CoreABC supports a comprehensive assembler-based configurable instruction set architecture and extensive and flexible configuration of size and feature options allowing it to be tuned to meet the resource constraints and processing power requirements of a wide variety of applications. The instructions executed are either held in a small internal ROM constructed from logic tiles ("hard" configuration), stored in RAM blocks internal to CoreABC ("soft" configuration), or in Fusion or SmartFusion devices, in on-chip nonvolatile memory ("NVM" configuration). The core is easy to configure and program offering efficient local control for use in real-time applications in Microsemi FPGAs.

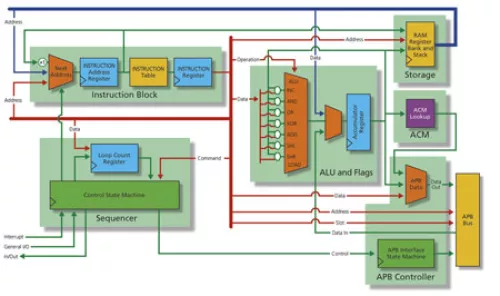

The core consists of six main blocks:

* Instruction block

* Sequencer

* ALU and flags

* Storage

* ACM

* APB controller

* AMBA3 APB master interface controller

Simple Micro APB Bus Controller

Overview

Key Features

- Programmable APB bus controller

- Hard, soft (RAM), or NVM instruction storage on Fusion devices; hard instruction storage on SmartFusion2, IGLOO2, RTG4, and PolarFire devices; hard or soft instruction storage on other device families

- Automatic detection of CoreAI in CoreABC’s APB address space and auto-creation of analog configuration MUX (ACM) data, based on CoreAI configuration

- Extensive configurability, allowing very low cost and resource efficient implementations

- APB interface can be configured for 8, 16, or 32-bit data

- In NVM instruction storage mode, APB data type read and write access to the instruction store memory (through an APB slave interface) is supported

- Built in general purpose input/output (GPIO) signals

- Interrupt driven operation using interrupt request and interrupt active signals

Block Diagram