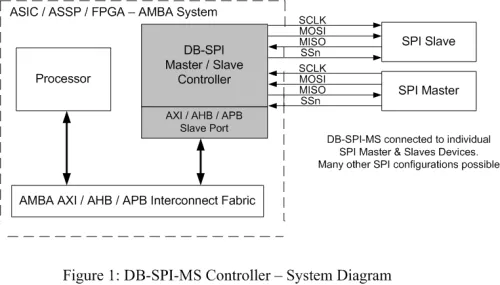

The Digital Blocks DB-SPI-MS is a Serial Port Interface (SPI) Controller Verilog IP Core supporting both Master/Slave SPI Bus transfers. The DB-SPI-MS contains an AMBA AXI, AHB, or APB Bus Interface for interfacing a microprocessor to external SPI Master/Slave devices.

The DB-SPI-MS contains Transmit/Receive FIFOs and Finite State Machine control with status & interrupt capability to fully off-load from the microprocessor the transfer of data over the SPI Bus. Optionally, the user can transfer transmitted or received data from the SPI Bus to user memory via an optional DMA Controller.

SPI Master / Slave Controller w/FIFO (APB Bus)

Overview

Key Features

- Master and Slave SPI Modes

- Full Duplex Transfers – Simultaneous Transmit & Receive

- Four Signal Interface:

- MOSI - Master Output, Slave Input (Data)

- MISO - Master Input, Slave Output (Data)

- SCK - Serial Clock

- SS[N:0] - Slave Select

- Up to N=8 Slave Select (SS) Outputs for multiple Slaves on SPI Bus

- Configurable SPI Modes:

- Standard SPI Mode (1 Data Lane)

- Dual SPI Mode (2 Data lanes)

- Quad SPI Mode (4 Data Lanes)

- Programmable SPI Frame Formats:

- Programmable inter-frame gap

- Programmable LSB-first or MSB-first frames

- Configurable FIFO depth for off-loading the SPI transfers from the processor:

- Separate Transmit / Receive FIFOs

- Optional DMA Controller for transfers between User Memory & SPI Bus

- Enhanced Error Detection & Protection

- Internal interrupts with masking control

- Clock Generator - Master Mode:

- Two Clock Sources

- Programmable Baud Rate

- Programmable Clock Phase & Polarity

- Master / Slave Independent Clock Domains

- Available AMBA Microprocessor Interfaces:

- AXI / AHB / APB Buses

- 8 / 16 / 32 bit Data Interface

- Compliance with ARM AMBA and Freescale / Motorola SPI specifications:

- Fully-synchronous, synthesizable Verilog RTL core, with rising-edge clocking, no gated clocks, and no internal tri-states, for easy integration into FPGA or ASIC design flows.

Benefits

- The DB-SPI-MS-APB Controller IP Core targets embedded processor applications with high performance algorithm requirements. While most SPI controllers require high processor interaction involvement, the DB-SPI-MS-APB contains a parameterized FIFO and Finite State Machine Control for the processor to off-load the SPI transfer to the DB-SPI-MS-APB Controller. Thus, while the DB-SPI-MS-APB is busy, independently controlling the SPI Transmit or Receive transaction of data, the processor can go off and complete other tasks.

Block Diagram

Deliverables

- Verilog or VHDL RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

Chartered, IBM, LSI. OKI, Silterra, SMIC, STMicroelectronics, Tower, TMSC, UMC

Maturity

Successful in Customer Implementations

Availability

Immediately