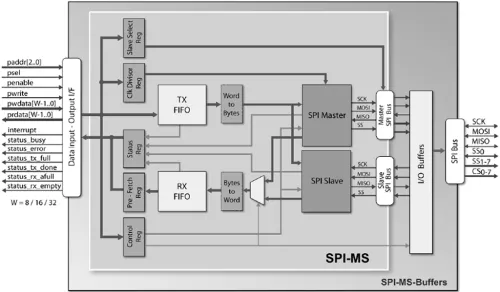

The SPI-MS core from Alma Technologies implements a Serial Peripheral Interconnect interface controller, which can operate either as a Master or a Slave. The Serial Peripheral Interface (SPI) allows high-speed synchronous serial data transfer between microprocessors / microcontrollers and peripheral devices.

When operating in master mode, the core generates the Serial data Clock (SCK) and selects the slave device which will be accessed. When operating in Slave mode, another master device generates the SCK and activates the slave select input of the core to signal communication.

The SPI Slave was carefully designed to provide the most reliable communication possible. The design is fully synchronous and has one clock domain, the system clock. No special technology features are used, so the RTL source code can be easily transferred to any technology. Other features incorporated in the core are the support for 8 Slave Select lines used to access up to 8 devices when working as a master. The ability to program the transfer order of the bits, MSB first or LSB first, is also implemented.

Serial Peripheral Interconnect Master & Slave Interface Controller

Overview

Key Features

- Run-time programmable Master or slave mode operation.

- Bit rates generated in Master mode: ÷2, ÷4, ÷6, ÷8, ÷10, ÷12, ...÷512 of the system clock.

- Bit rates supported in Slave mode: fSCK ≤ fSYSCLK ÷4

- Support for 1,2,4 or unlimitted bytes multi-byte frame data transfers, run-time programmable.

- Support for partial word transfer in 2, 4 or unlimited multi-byte frame modes.

- 8 Slave Select lines.

- 8 Chip Select lines.

- Configurable RX and TX FIFOs.

- Little or Big Endian byte mapping in multi-byte frames.

Block Diagram

Applications

- Interfacing to sensors, ADC/DAC, memories, flash cards and other peripherals using the SPI protocol

Deliverables

- Clear text VHDL or Verilog RTL source for ASIC designs, or pre-synthesized & verified Netlist for Altera, Lattice, Microsemi and Xilinx FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Self checking testbench environment, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Technical Specifications

Maturity

Silicon Proven

Availability

NOW

Related IPs

- SG DMA Controller, 1-16 DMA Channels, AHB5 Master Interface

- Serial Peripheral Interface – Master/Slave with Octal, Quad, Dual and Single SPI Bus support

- APB SPI (Serial Peripheral Interface) master and slave

- A bridge to convert the slave SPI interface to the master I2C interface and vice versa

- A bridge to convert the slave SPI interface to the master UART interface and vice versa

- I2C Bus Master / Slave Controller Interface with FIFO