MIPI-I3C Combo IP Host/Target HDR-DDR compliance with Spec v1.1.1

Overview

MIPI I3C(Improved Inter Integrated Circuit) is a two-wire bidirectional serial Bus for sensors communication. The MIPI I3C interface has been developed to ease sensor system design architectures in mobile sensor and IoT / automotive sensor wireless products by providing a fast, low cost, low power.

Key Features

- Compliance as per MIPI I3C - V.1.1.1 Release .

- Two wire serial interface up to 12.5 MHz using Push-Pull and open drain

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices.

- Support Single Data Rate messaging(SDR).

- Support Broadcast and Direct Common Command Code (CCC) Messages.

- In-Band Interrupt support.

- Hot-Join support.

- Synchronous Timing Support and Asynchronous Time Stamping.

- HDR Double Data Rate (HDR-DDR) Mode

- HDR Exit Pattern

- HDR Restart Pattern

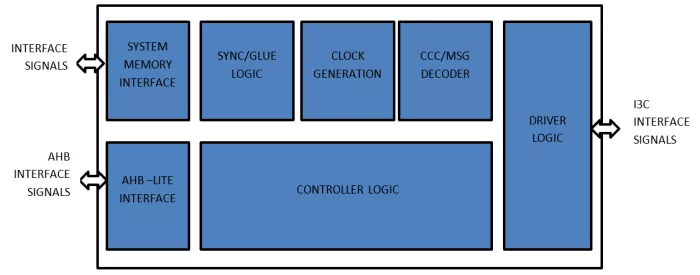

Block Diagram

Applications

- Consumer Electronics.

- Defense.

- Aerospace.

- Virtual Reality.

- Augmented Reality.

- Medical.

- Biometrics (Finger prints, etc).

- Automotive Devices.

- Sensor Devices.

Deliverables

- Verilog Source code.

- User Guide.

- IP Integration Guide.

- Run and Synthesis script.

- Encrypted Verification Testbench Environment.

- Basic Testsuite

Technical Specifications

Availability

immediate

Related IPs

- MIPI-I3C Combo Host and Target interface controller IP for Sensor and Peripheral connection

- MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- SD Host Controller IP, SD host spec. v3.0, SDIO spec. v2.0, MMC spec. v4.3, Supports UHS50/UHS104 card, Soft IP

- Active antenna detector with load current limit and supply current 140 uA

- Active antenna detector with load current limit

- Intermediate frequency amplifier with wide gain range