Low-Power Bandgap Reference - Low Integrated Noise (62.5µVrms) in TSMC 40nm

Overview

This macro-cell is a low power voltage reference generator core designed for TSMC 40nm CRN40LP CMOS technology. The core is ideal as a general purpose reference voltage in applications where low output noise and wide PSRR band are critical. The circuit generates an unbuffered 547mV, temperature compensated bandgap voltage reference (62.5ppm/ C). Internal start-up circuit allows the reference is available as soon as the power supply ramps up, so none enable/disable function is necessary to start it up. It has three trimming bits for the coeficient temperature. It has a general purpose 800nA PTAT output current. The core is easily re-targeted to any other CMOS technology.

Key Features

- Low power (LP) bandgap reference

- Vref=0.547V ±2.8% (without trimming)

- 5uA current consumption in active mode

- Supply voltage: 1.0–1.32V

- Output noise: 62.5uVrms (integrated up to 20MHz)

- PSRR 42dB @ 20MHz

- Automatic start-up as soon as power supply starts

- Indicative area: 0.051mm2

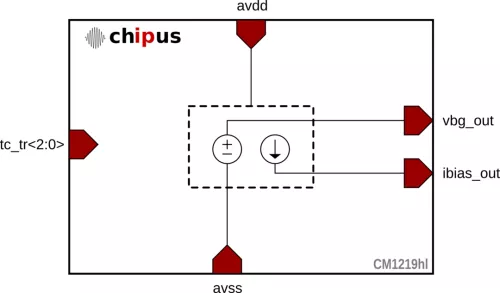

Block Diagram

Applications

- Voltage Reference for ADCs

Deliverables

- Datasheet/Integration Guide

- HDL Model

- Flat GDSII database/LVS netlist

- Customer Support

Technical Specifications

Foundry, Node

TSMC 40nm

Maturity

Silicon Available

Silterra

Pre-Silicon:

180nm

TSMC

Pre-Silicon:

40nm

LP

Related IPs

- Bandgap Voltage Reference - Low Integrated Noise (57.2µVrms) TSMC 40nm

- Low-Power, High-Accuracy, Bandgap Reference in GF22FDX

- Low-Power Bandgap Reference Circuit - UMC 0.09um

- Low-Noise Bandgap Reference - Low Noise: 63nV/?Hz, PSRR: -80dB TSMC 0.18um CMOS (CLM18)

- Ultra-Low-Power Bandgap Voltage Reference in 40nm CMOS

- Low-power, High-Precision Voltage Band-Gap Reference Circuit