Low-Power 10-bit SAR ADC - 10 bits, 240kSPS, 8 multiplexed inputs LFoundry 0.15 um

Overview

This macro-cell is a general purpose, 10-bit, 240kSPS, 8-multiplexed input Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) core designed for LFoundry 0.15µm LF150 CMOS technology STD (Standard) and LP (Low Power) process. The circuit occupies a small area and is optimized for low power consumption. The core is easily retargeted to any other CMOS technology with R-poly devices.

Key Features

- General purpose SAR ADC

- 10-bit resolution

- 240kSPS speed

- avdd = 3.3V, dvdd = 1.8V

- INL = ±0.5 LSB, DNL = ±0.5 LSB

- Indicative area: 0.12mm2

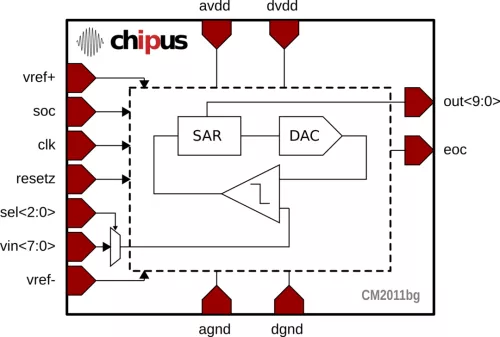

Block Diagram

Applications

- Housekeeping

- Monitor applications

- Consumer electronics

- Tuning machines

- Silicon Under Tests

Deliverables

- Datasheet/Integration Guide

- HDL Model

- Flat GDSII database/LVS netlist

- Customer Support

Technical Specifications

Foundry, Node

LFoundry 0.15 um

Maturity

Silicon Available

LFoundry

Pre-Silicon:

150nm

Related IPs

- General Purpose 10-bit DAC - 10 bits, 2MSPS, buffered output option LFoundry (SMIC) 0.15 um

- 10-bit 1-channel 10 to 150 MSPS SAR ADC

- 8 bit SAR ADC

- 130kHz Internal Oscillator - Low voltage (1V), Low Power (160nW@130kHz) LFoundry (SMIC) 0.15 um

- 10-bit 1-channel 1 MSPS SAR ADC

- 750mV Voltage Reference - Ultra Low Voltage (1V), Ultra Low Power (400nW) LFoundry 0.15 um