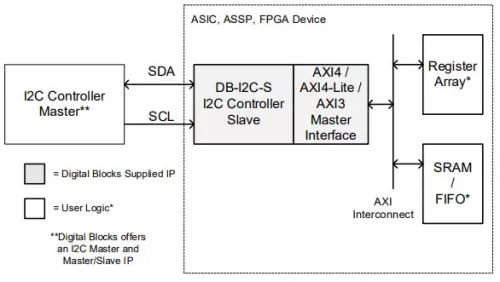

The DB-I2C-S-AXI-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required). The DB-I2C-S-AXI-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge AXI Master Interface to user registers or memory.

The DB-I2C-S-AXI-BRIDGE runs off the AXI Master external clock input within the ASIC / ASSP, providing a synchronous design while offering I2C spike filtering of SDA and SCL.

I2C Slave with AXI Master Bridge (I2C2AXI4)

Overview

Key Features

- I2C Slave Controller - Implements Slave-only protocol for smaller VLSI footprint, for applications requiring Slave–Receiver and Slave–Transmitter capability

- AXI Master Interface – bridging the I2C Bus to the AXI Bus

- Autonomous I2C Slave Controller:

- No local CPU host required

- No configuring of control/status registers

- Slave I2C Controller Modes:

- Slave – Transmitter

- Slave – Receiver

- Supports five I2C bus speeds:

- Standard Mode (100 Kb/s)

- Fast Mode (400 Kb/s)

- Fast Mode plus (1 Mbit/s)

- Ultra fast mode (5 Mbit/s)

- Hs-mode (3.4 Mbit/s)

- 7- or 10-bit I2C Slave ID addressing, SCL Low Wait States

- Digital filter for the received SDA and SCL lines

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

Chartered, Global Foundries, Intel, LSI. OKI, Silterra, SMIC, STMicroelectronics, Tower, TMSC, UMC

Maturity

Successful in Customer Implementations

Availability

Immediately

Related IPs

- A bridge to convert the slave SPI interface to the master I2C interface and vice versa

- I2C Master / Slave Controller with FIFO (AXI & AXI-Lite Bus)

- I2C Slave with APB Master Bridge (I2C2APB)

- I2C Slave with AHB Master Bridge (I2C2AHB)

- I2C Slave To AXI Bridge IIP

- I2C Master / Slave Controller w/FIFO (AXI & AXI-Lite Bus)