The LatticeSCM Ethernet flexiMAC™ MACO™ IP core is a flexible packet framer and parser that can implement Layer2 (data link layer or MAC) functionality for various standards. The flexiMAC functionality complements the Layer1 (physical layer) multi-protocol functionality of the LatticeSCM Physical Coding Sublayer (PCS) and is implemented in MACO hard logic. This yields a complete Layer1/Layer2 solution for 1/10Gb Ethernet standards.

The flexiMAC core assists the FPGA designer’s efforts by providing pretested, reusable functions that can be easily plugged in, freeing designers to focus on their unique system architecture. These blocks eliminate the need to “re-invent the wheel,” by providing either an industry-standard Layer 2 flexible packet framer and parser or a Layer 1 multi-protocol functionality of the Physical Coding Sublayer (PCS) module. This proven core is optimized utilizing the LatticeSCM device’s MACO architecture, resulting in fast, small cores that utilize the latest architecture to its fullest.

Software Requirements

* ispLEVER version 7.0 or later

* MACO design kit

* MACO license file

Ethernet 1G/10G flexiMAC MACO Core

Overview

Key Features

- 1Gb Ethernet MAC (full duplex only) standard support.

- 10Gb Ethernet MAC standard support including clauses 46.3.3 (Error and Fault Signaling) of IEEE Draft P802.3ae (also known as reconciliation layer)

- IP provided in encrypted netlist

- ModelSim® simulation models and test benches available for free evaluation

- In 10Gb Ethernet mode, the TX flexiMAC will frequently back-pressure the TX client when there are less than two client clock (156MHz) cycles between consecutive packets written to the TX EBR interface. Similarly, 10Gb Ethernet mode requires a minimum Inter-Packet Gap (IPG) of 16 bytes between incoming RX XAUI packets if the client side of the MAC is to perform an RX to TX loopback.

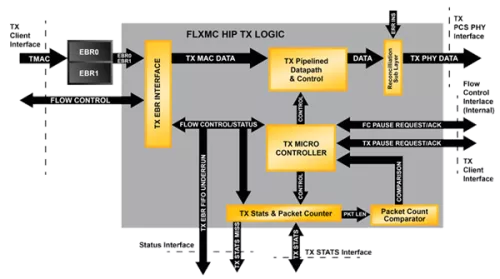

Block Diagram

Technical Specifications

Related IPs

- 1G/10G/25G/50G/100G Ethernet Switch IP Core - Efficient and Massively Customizable

- 10/25/40/100G MAC/PCS Ethernet IP Core

- Ethernet Switch 1G/10G

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network