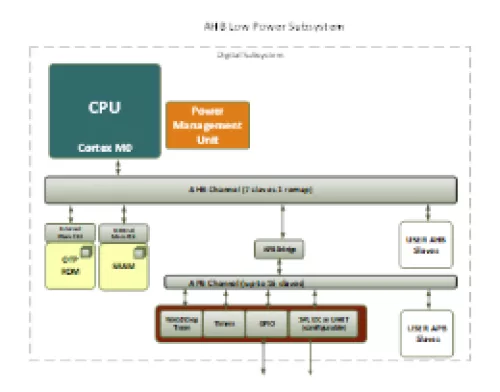

The AHB Low Power Subsystem is an AMBA® based system that is useful as the basic digital infrastructure for building low power SOCs. The subsystem contains a flexible Power Management Unit that controls the power sequence of the CPU as well as the APB peripherals. The PMU can easily be extended to control additional cores, peripherals and even mixed signal subsystems on the same SOC.

The AHB Low Power Subsystem includes a standard set of peripherals and cores that supports RTOS and software kernels. The package includes software for boot code, interrupt handlers and driver code.

The AHB Low Power Subsystem is soft IP that can be used in all the popular semiconductor technology nodes.

AHB Low Power Subsystem - ARM M0

Overview

Key Features

- Supports Cortex-M0 (or equivalent) processor.

- AMBA® 3.0 (AHBLite)

- AHB/APB Bus infrastructure

- Standard APB Peripheral package

- Power Management Unit

- 8,16,32-bit Internal SRAM Controller

- Watchdog Timer, Timers (2), GPIO

- Configurable

- I2C Master, SPI Master / Slave, 16550 UART

- Software

- Boot Code

- Basic Kernel

- Hardware Adaption Layer / Drivers

- SPI, I2C, GPIO

Benefits

- Quick design start

- Integration expertise and support

- Hardware/Software and application support

- Cost effective

Block Diagram

Applications

- IoT Edge Devices

- Small Controllers

- Mixed Signal Digital - MEMS

- Smart Sensors

- Smart Lighting

- Health Monitors

- Power Management

- Industrial Sensors

Deliverables

- Verilog RTL source code

- Test bench with test suites

- Documentation including User's Guide and Integration Guide

- Technology-independent synthesis constraints

Technical Specifications

Foundry, Node

all

Maturity

Silicon Proven

Availability

Now