The AES encryption IP core implements Rijndael encoding and decoding in compliance with the NIST Advanced Encryption Standard. It processes 128-bit blocks, and is programmable for 128-, 192-, and 256-bit key lengths.

Two architectural versions are available to suit system requirements. The Standard version (AES-S) is more compact, using a 32-bit datapath and requiring 44/52/60 clock cycles for each data block (128/192/256-bit cipher key, respectively). The Fast version (AES-F) achieves higher throughput, using a 128-bit datapath and requiring 11/13/15 clock cycles for each data block.

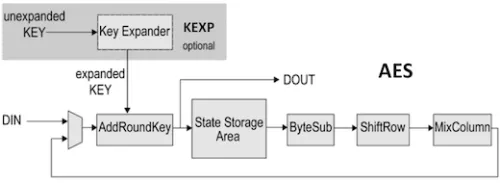

Various cipher modes can be supported (ECB, CBC, OFB, CFB, CTR, CCM, GCM and LRW). The core works with a pre-expanded key, or with optional key expansion logic.

The AES core is a fully synchronous design and has been evaluated in a variety of technologies. It is available optimized for ASICs or FPGAs, with complete deliverables.

AES Encrypt/Decrypt Core

Overview

Key Features

- Encrypts and decrypts using the AES Rijndael Block Cipher Algorithm

- Implemented according to the Federal Information Processing Standard (FIPS) Publication 197 from the US National Institute of Standards and Technology (NIST)

- NIST Certified

- Processes 128-bit data in 32-bit blocks

- Employs user-programmable key size of 128, 192, or 256 bits

- Smallest version supports a single block cipher mode, Electronic Codebook (ECB); these modes can be added as needed:

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR)

- Counter with CBC-MAC (CCM)

- Galois/Counter (GCM) and

- Liskov-Rivest-Wagner (LRW)

- Two architectural versions:

- Standard is more compact:

- 32-bit data path size

- Processes each 128-bit data block in 44/52/60 clock cycles for 128/192/256-bit cipher keys, respectively

- Fast yields higher transmission rates:

- 128-bit data path

- Processes each 128-bit block in 11/13/15 clock cycles for 128/192/256-bit cipher keys, respectively

- Works with a pre-expended key or can integrate the optional key expansion function

- Simple, fully synchronous, reusable design

- Available as fully functional and synthesizable VHDL or Verilog, or as a netlist for popular programmable devices

- Complete deliverables include test benches, C model and test vector generator

Block Diagram

Applications

- Protected network routers

- Electronic financial transactions

- Secure wireless communications

- Secure video surveillance systems

- Encrypted data storage

Deliverables

- HDL RTL source code (ASICs) or post-synthesis EDIF netlist (FPGAs)

- Sophisticated HDL Testbench (self checking)

- C Model & test vector generator

- Simulation script, vectors & expected results

- Synthesis script

- User documentation

Technical Specifications

Maturity

Production Proven

Availability

Now

Related IPs

- Programmable Mode AES Encrypt/Decrypt Core

- DPA and FIA-Resistant Ultra-Compact FortiCrypt AES IP core

- DPA- and FIA-Resistant Balanced FortiCrypt AES IP Core

- DPA- and FIA-resistant Ultra High Bandwidth FortiCrypt AES IP core

- DPA- and FIA-resistant Ultra Low Power FortiCrypt AES IP core

- AES Encrypt/Decrypt 128/192/256