Rambus Crypto Accelerator AES-AE–Fast Hardware Cores offload compute intensive cryptographic algorithms in SoC’s CPU at 100x performance (when run at identical frequencies) and 10% of the power consumption compared to running the same algorithms in software.

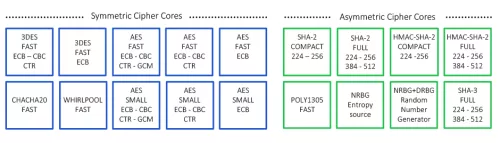

The Crypto Accelerator Hardware Cores offer chipmakers an easy-to-integrate technology-independent soft-macro security solution, offering various levels of cryptographic acceleration performance.

They are easy to integrate into various SoC and FPGA architectures and development flows, and are all designed to maximize performance versus silicon area requirements. The Rambus IP core pass all NIST CAVP vectors. Several of the cores are also available in Differential Power Analysis (DPA) protected versions, extensively validated using the standardized Test Vector Leakage Assessment (TVLA) methodology. These Crypto accelerator cores are portable to any FPGA or ASIC technologies.

AES-ECB 1 Billion Trace DPA Resistant Crypto Accelerator

Overview

Key Features

- Superior performance cryptographic cores optimized for performance, area, and security applications

- Technology and node independent RTL source code design

- Synchronous design and interface allows easy integration in various SoC architectures

Benefits

- Superior Cryptopraphic protection

- Use with any ASIC or FPGA Technology and node independent

Block Diagram

Applications

- Government, Automotive, Military, Edge, IoT, Machine Learning (ML), Artifical Intelligence (AI), Semiconductor, Processors, Cryptocurrency

Deliverables

- Configurable Cryptographic Core: Verilog RTL reference design

- Synthesis Inputs: SDC constraint file suitable for FPGA or ASIC synthesis

- Full Documentation: Specification documents and Integration guides

- Functional Testbench: NIST-compliant test vectors

Technical Specifications

Foundry, Node

Any

Maturity

In production

Availability

Now

Related IPs

- AES-ECB 1 Billion Trace DPA & Fault Injection Resistant Crypto Accelerator

- AES-ECB-CBC-CFB-CTR 1 Billion Trace DPA Resistant Crypto Accelerator

- AES-ECB-CBC-CFB-CTR-GCM 1 Billion Trace DPA & Fault Injection Resistant Crypto Accelerator

- AES-ECB-CBC-CFB-CTR-GCM 1 Billion Trace DPA Resistant Crypto Accelerator

- ChaCha20 DPA Resistant Crypto Accelerator

- HMAC-SHA-2 (224/256/384/512) 100 Million Trace DPA Resistant Crypto Accelerato