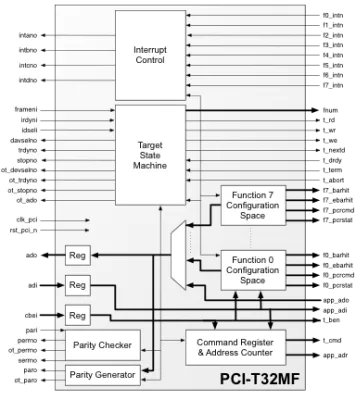

The PCI-T32MF implements a target-only PCI interface compliant with the PCI 2.3 specification. It supports a 32-bit address/data bus and operates up to 33 MHz (PCI clock).

The core offers one to eight independent PCI functions in a single chip, each implementing 64 to 256 bytes of PCI Configuration Space registers as required. Each function supports up to six Base Address Registers, with both I/O and Memory space decoding from 16 bytes up to 4GB.

The core was developed for easy reuse with ASICs or FPGAs.

32-bit, 33 MHz Multifunction Target Interface

Overview

Key Features

- Flexible synthesizable VHDL core

- PCI specification 2.2 compliant

- 33 MHz performance

- 32-bit datapath

- Zero wait states burst mode

- Full Target functionality

- All interrupt pins support (INTA#, INTB#, INTC#, INTD#)

- Type 0 Configuration space

- Support of all Base Address Registers

- Support of backend initiated target retry, disconnect and abort

- Parity generation and parity error detection.

- Available in synthesizable VHDL source code

- Verified in a XILINX Virtex FPGA

- PC300 prototyping board available for fast application prototyping

Benefits

- Isolates the user from having to solve complex problems of the PCI implementation and lets the user instead focus on the application development

- Supports 32-bit address/data bus and operates up to 33 MHz (PCI clock frequency)

- Fully compliant with the PCI Local Bus Specification, Revision 2.2.

- Target-only PCI Interface core

- Offers implementation of 1 to 8 independent PCI functions in a single chip

- Each function implements 64 bytes of PCI Configuration Space registers

- Possible to extend the Configuration Space up to 256 bytes if required

- Each function supports up to six Base Address Registers with both I/O and Memory space decoding from 16 bytes up to 4GB.

- The Target supported commands are:

- Configuration Read, Configuration Write

- Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL), Memory Write and Invalidate (MWI)

- I/O Read, I/O Write

Block Diagram

Deliverables

- VHDL RTL source code

- Testbench

- Vectors for testbench

- Expected results for testbench

- Simulation and synthesis scripts

- Documentation

Technical Specifications

Maturity

Production Proven

Availability

Now