Other for TSMC

Welcome to the ultimate Other for TSMC hub! Explore our vast directory of Other for TSMC

All offers in

Other

for TSMC

Filter

Compare

5

Other

for TSMC

from 4 vendors

(1

-

5)

-

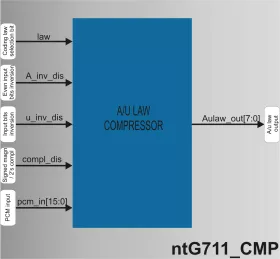

ITU G.711 compressor

- Compresses 16-bit linear PCM to 8 bit a-law or u-law logarithmic PCM.

- Compliant to the ITU G.711 standard.

- Purely combinational logic RTL implementation.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

-

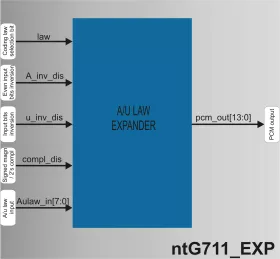

ITU G.711 expander

- Expands 8 bit a-law or u-law logarithmic PCM to 13/14 bit linear PCM.

- Compliant to the ITU G.711 standard.

- Purely combinational logic RTL implementation.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

-

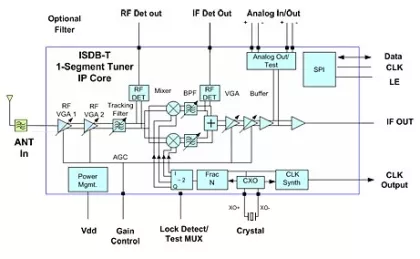

ISDB-T1, Segment Tuner (470-860MHz UHF)

- High Performance

- Configurable 3/4 wire controller

- Self calibrating and programmable filter corner frequencies

- 8 Bit electronically tunable tracking filter

-

Single-core video encoder - AV1, HEVC, AVC

- YUV420/YUV422/YUV444

- 8/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances

-

MIPI D-PHY/sub-LVDS/CMOS1.8 combo Transmitter 2.5G/800Mbps 8-Lane

- MIPI DPHY v1-2 / MIPI CSI2 compliant

- Differential signal of almost CIS serial outputs support

- Xtal Input Clock Frequency Selectable: 24 - 72MHz

- Input Clock Frequency: