eFPGA IP

Welcome to the ultimate eFPGA IP hub! Explore our vast directory of eFPGA IP

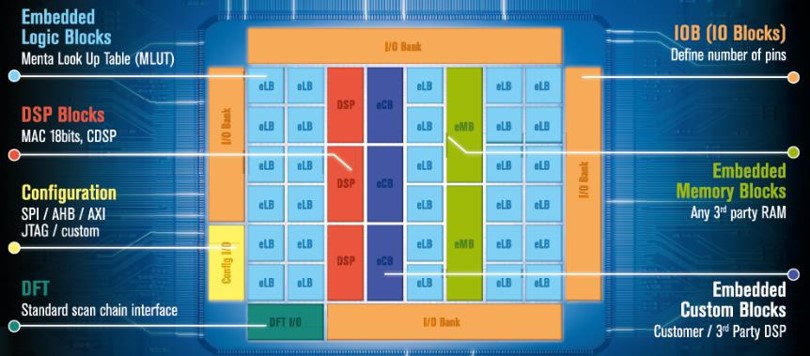

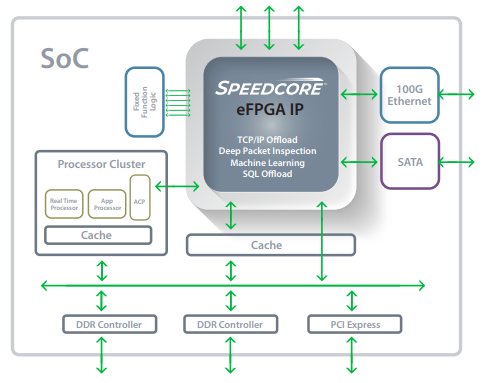

An eFPGA (embedded FPGA) is an IP core that is embedded within a custom ASIC or SoC. The IP can be licensed for use similar to that of other IP used in semiconductor designs. Unlike a standalone FPGA, eFPGA IP designers can select the exact amount of logic, DSP (or MLP) and memory resources required for their application. An eFPGA instance can also be used when flexibility is needed while lowering system cost, power and board space by eliminating the excess features of the standalone FPGA which are not required when moving into high-volume production.

All offers in

eFPGA IP

Filter

Compare

14

eFPGA IP

from 6 vendors

(1

-

10)

-

eFPGA IP - 100% third party standard cells

- Every element of the eFPGA can be defined in numbers: logic cells, adaptive DSP (with and without FIR engine, add & mult size, amount), RAM (type and amount) and IOs.

- In addition, Menta eFPGA IP Cores being 100% standard cells based, multiple power / performances trade-off can be achieved based on customer requirements.

- The eFPGA IP Cores are provided as hard IPs (GDSII).

- Menta eFPGA IP Cores use standard cells, and as such integrate smoothly into any standard ASIC design flow. Designers use RTL as the input to our software Origami Programmer to generate the eFPGA program file (bitstream) and obtain accurate performance evaluation.

-

eFPGA

- Customize Vega to suit your needs

- Accelerate your processor with Vega eFPGA

- Seamlessly integrate and verify Vega IP into your SoC design

- Enhance flexibility with on-chip FPGA functionality

-

eFPGA IP and FPGA Software Built on GLOBALFOUNDRIES 22FDX

- High-performance architecture for low power applications

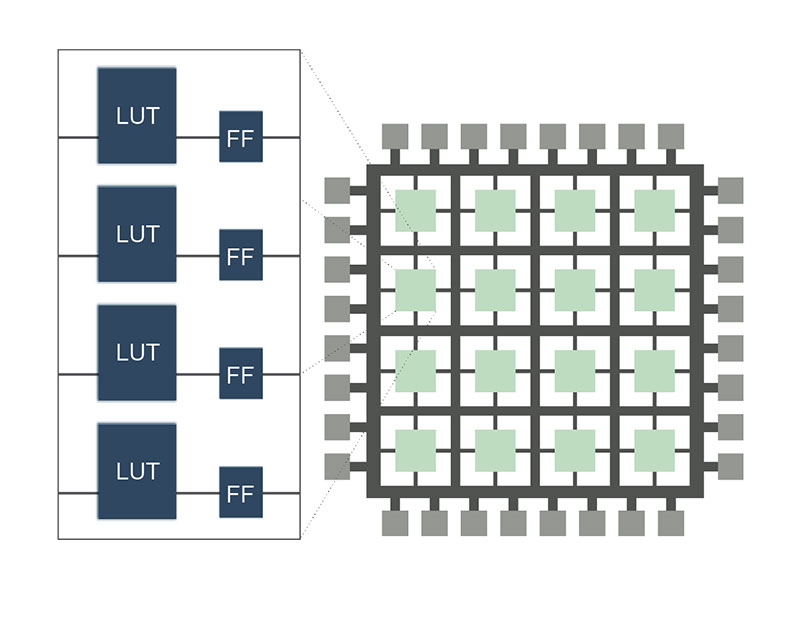

- Super Logic Cell (SLC) clusters 4 logic cells together with hierarchical routing networks for optimum performance and power consumption

- Each logic cell can be used as two separate 4-input LUTs or one 5-input LUT.

- Direct input selection to the register allows combinatorial and sequential logic to be used separately.

-

65nm/40nm Low Power eFPGA IP and Open Source FPGA Software

- Flexibility

- Lower R&D Costs

- Increase Performance

-

Embedded FPGA

- 75% lower power

- 90% lower cost

- 100× lower latency

-

Embedded FPGA

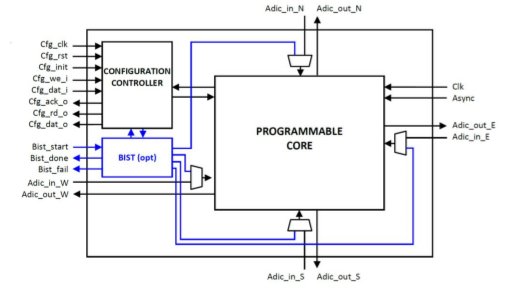

- Fully integrated into RTL SOC design flow

- Highly scalable and customizable

- Technology independent

-

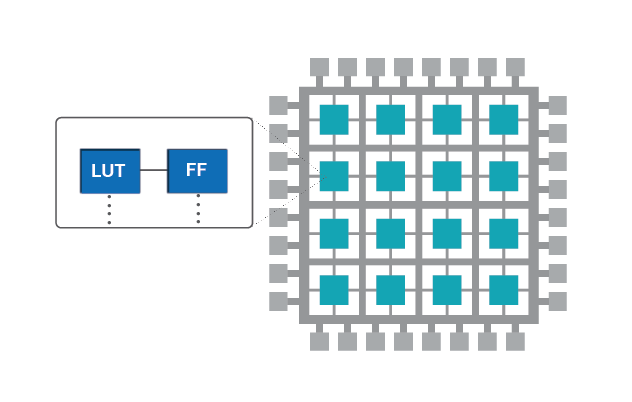

eFPGA IP as a synthesizable RTL core

- Support of any technology node, foundry and process option

- High LUTs density

- Support of any kind of arithmetic block right within the IP

-

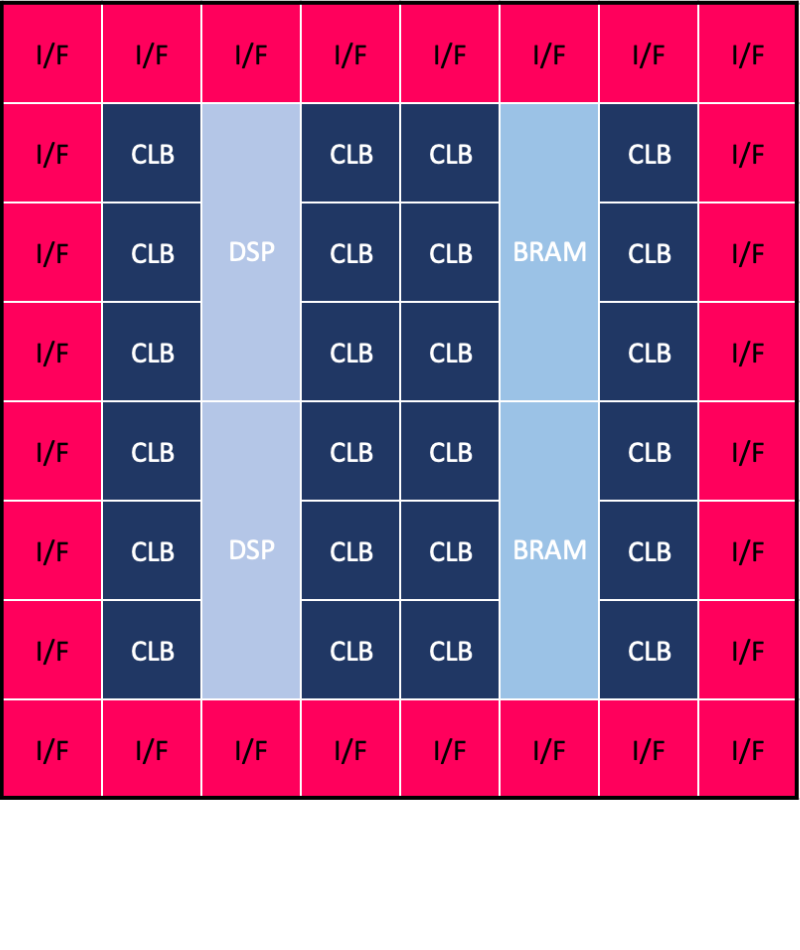

EFLX eFPGA family overview

- High density & high performance similar to commercial FPGA

- eFPGA Arrays of any size by tiling proven eFPGA IP Logic, DSP or I/O tiles

- Compatible with most metal stacks. Integrate RAM between tiles

- Optimizable for super-low power or super-high performance