Fractional-N PLL is a multi-function, general purpose frequency synthesizer. Ultra-wide input and output ranges along with excellent jitter performance, modest area, and application-appropriate power allow the PLL to be configured for almost any clocking application of complex SoC environments.

Ultra-low Jitter Fractional-N Frequency Synthesizer PLL (5nm - 180nm)

Overview

Key Features

- Jitter-Power optimized to meet PCIe1-5 reference clock requirements

- Wide functional range

- 24 bit fractional resolution so output frequency is programmable in steps less than 0.01ppm

- Noise Cancellation DAC enables ultra-low jitter in fractional mode -- better than "Low jitter" integer PLLs from many others

- Pairs with DPLL digital loop filter to construst a Jitter Cleaner PLL

- Small footprint

- Optional Spread Spectrum clock generation capability

Benefits

- Jitter-Power optimized to meet PCIe1-5 reference clock requirements - replaces 300mW/$2.50 clock chip

- Low area on chip -- keepouts = DRC limit in most cases

- Self biased and automatically adjusts for any input frequency, so no complicated programming is required

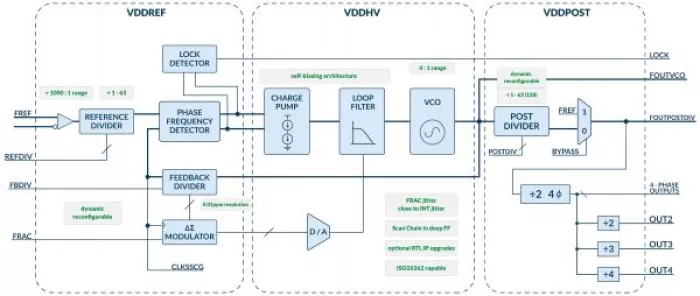

Block Diagram

Applications

- SerDes reference clock

- AFE/ADC/DAC reference clock

Deliverables

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note

Technical Specifications

Foundry, Node

TSMC -- 5nm to 40nm

Maturity

Production

Availability

Available Now

Renesas

In Production:

90nm

TSMC

In Production:

12nm

,

16nm

,

28nm

Pre-Silicon: 5nm

Silicon Proven: 7nm , 40nm G

Pre-Silicon: 5nm

Silicon Proven: 7nm , 40nm G

Related IPs

- Very Low Area Fractional-N Frequency Synthesizer PLL

- Fractional-N Frequency Synthesizer PLL

- High Performance Fractional-N RF Frequency Synthesizer PLL in UMC 40LP

- High Performance Fractional-N RF Frequency Synthesizer PLL in GlobalFoundries 22FDX for 5G, WiFi, etc

- High Performance Fractional-N RF Frequency Synthesizer PLL in Samsung 8LPP for 5G, WiFi, etc

- High Performance Fractional-N RF Frequency Synthesizer PLL in Samsung 14LPP for 5G, WiFi, etc