TESIC CC EAL5+ Secure Element IP Core

Overview

TESIC is a CC EAL5+ PP0084 & PP0117 proven/certification-ready secure element IP that is delivered as hard macro for plug-and-play System-on Chip (SoC) integration

Key Features

- CC EAL5+ secure microcontroller system

- Secure microcontroller core (clockless or RISC-V)

- Secure memory Protection Unit (MPU)

- Timers (3)

- CC EAL5+ secure cryptography

- FIPS 197 compliant AES up to 256 bits

- FIPS 46-3 compliant DES/3DES with hardware CBC mode

- Public Key Accelerator

- ECC up to 521 bits

- RSA up to 4096 bits,

- SHA2 and SHA3 hardware accelerators

- CRC 16-bit, compliant with ISO/IEC 13239

- TRNG compliant with AIS-31 and FIPS140-2

- PRNG

- CC EAL5+ security sensors

- Glitch detectors

- Temperature sensor

- Active shield

- 4 phases hand-shake protocol

- Interfaces

- APB slave interface

- AHB master interface

- Secure GPIOs

- Secured standard JTAG TAP for test

- ISO 7816 slave interface for integration of SoC test framework

- Option

- NFC ISO 14443 for admin interface or payment

Benefits

- Targeted designs are SoCs that require a security enclave highly protected against side-channel attacks and perturbation/fault attacks, and that execute secure software such as iSIM, EMVCo payment, FIDO2 Web authentication, V2X HSM protocol and/or other security routines for the SoC system, including secure boot, secure OTA firmware update, secure storage and secure debug.

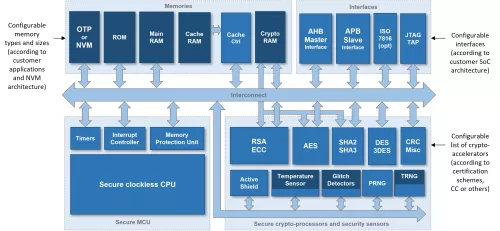

- TESIC includes a secure MCU, secure cryptographic processors and hardware accelerators, security sensors, secure memories and standard interfaces for easy integration and test. Memory sizes, cryptographic accelerators and interfaces can be customized according to customer requirements.

- TESIC supports any non-volatile memory (NVM) architecture, including embedded flash and MRAM, and the use of any external flash chip. It implements a security protocol for the encrypted communication and secure storage with any external flash that is CC EAL5+ PP0117 compliant.

Block Diagram

Applications

- JavaCard 3.0.5 OS

- Connectivity iSIM (iUICC)

- Payment (EMVCo)

- Web authentication (FIDO 2)

- Automotive PP V2X HSM

- Automotive Smart Car Access

Deliverables

- TESIC is delivered as a GDS hard macro to the certified fab, with the guarantee to pass CC EAL5+ PP0084 & PP0117 and/or EMVCo security certification of the chip integrating this macro. It is available on multiple silicon processes, including GF 55 LPx, TSMC 40 ULP, GF 22 FDX and TSMC 16 FFC.

Technical Specifications

Foundry, Node

GF 55 LPx, TSMC 40 ULP, GF 22 FDX, TSMC 16 FFC

Maturity

Qualified and certified on various processes

Availability

Now

GLOBALFOUNDRIES

Pre-Silicon:

22nm

FDX

TSMC

Pre-Silicon:

16nm

Silicon Proven: 40nm LP

Silicon Proven: 40nm LP

Related IPs

- TESIC RISC-V CC EAL5+ Secure Element Soft/Hard Macro

- Integrated Secure Element (iSE) for multiple applications

- Integrated Secure Element (iSE)

- Integrated Secure Element (iSE) for automotive

- Integrated Secure Element (iSE) for industrial IoT, factory automation, and AI devices

- Integrated Secure Element (iSE) for high-end devices with HW isolated secure processing