Rambus Hardware Root of Trust RT-630-FPGA is a fully-programmable hardware security core offering security by design. It protects against a wide range of attacks through state-of-the-art anti-tamper and security techniques.

As cloud, artificial intelligence, and machine learning applications evolve, device architects are understandably concerned about emerging security threats. While these applications may differ, one constant is the need for a hardware root of trust-based security implementation.

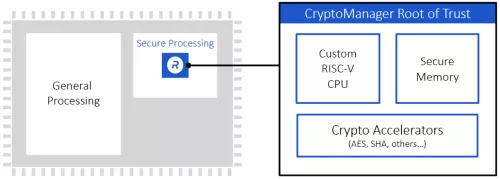

The Rambus RT-630 is the ideal security co-processor for these markets. The RT630 features our 32-bit RSIC-V siloed and layered secure co-processor, along with dedicated secure memories. The RT-630 also features a number of high-capability cryptographic accelerators like AES-AE-16, HMAC 512, RSA 4K, ECC 521, a NIST-compliant Random Bit Generator, AXI Multi Issue Out-of-Order, and Fast DMA. Satisfying use cases such as identity management, attestation, and secure boot, the RT-630 is ideally suited for cloud, AI and ML applications where security is a priority.

RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

Overview

Key Features

- Superior Security

- Hardware root of trust featuring a custom RISC-V processor

- Secure in-core processing and industry-leading anti-tamper

- Multi-layered security model provides protection of all components in the core

- FIPS 140-2 CAVP compliant

- Enhanced Flexibility

- 3rd-party applications run securely within trusted boundary

- Complete development environment allows users to easily develop secure applications

- Leveraging all capabilities of the core; standard use case containers provided

- Support for secure provisioning of keys and firmware at manufacturing or in the field

- Support multiple roots of trust within a single core

- Security Models

- Cryptographic Accelerators

- Security Modules

Benefits

- Secure co-processor

- Main processor agnostic

- Standard secure applications

- Technology and process node independent

Block Diagram

Applications

- Cloud, Artificial Intelligence, Machine Learning processors

Deliverables

- Verilog RTL Design database

- Tools and Scripts for synthesis and simulation

- Complete verification test bench and comprehensive set of test vectors

- Complete Documentation Set: Hardware Reference Manual, Integration Guide, HLOS Programmer’s Guide, Developer’s Guide, API Guide

- Boot loader and firmware, including secure RTOS and security monitor

- HLOS APIs for accessing capabilities

- Secure Application SDK with complete development environment, including compiler, assembler, debugger, simulator, reference code, container-authoring software

- QEMU implementation

- Implementation of HLOS or ASIC components

- Sample application demonstrating usage of Secure Application

Technical Specifications

Foundry, Node

Any

Maturity

In Production

Availability

Now

Related IPs

- RT-630 Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- RT-650 DPA-Resistant Hardware Root of Trust Security Processor for Govt/Aero/Defense FIPS-140

- RT-660 DPA & Fault Injection Resistant Hardware Root of Trust Security Processor for Govt/Aero/Defense FIPS-140

- Root of Trust eSecure module for SoC security

- Hardware Root of Trust IP

- Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine