Weebit ReRAM (Resistive Random Access Memory), is an innovative Non-Volatile Memory (NVM) technology that can be easily integrated into any CMOS IC. ReRAM combines the advantages of RAM and flash: it is non-volatile, extremely fast, low-power and cost-effective. The high-performance and ultra-low-power NVM achieves 10K programming cycles and 10 years’ retention at high temperatures.

The technology is available in SkyWater 130nm CMOS process. The technology is fully qualified, available for integration in users’ SoCs, and ready for production. The Weebit ReRAM IP module is provided in a wide range of capacities and features, and it can be customized per customer needs.

SkyWater’s 130nm technology node is a dual gate technology with 1.8V and 3.3V/5.0V devices. The technology supports up to five aluminum metal layers; and is mixed-signal enabled with native, extended drain, NPN and PNP BJTs, inductors, MIMs, etc. The technology offers a variety of thresholds to optimize for power and performance.

ReRAM NVM in 130nm CMOS, S130

Overview

Key Features

- Technology: 130nm, SkyWater S130

- Mask Adder: 2

- Supply Voltage: 1.8V Read, 1.8V+3.3/3.6V Program

- Read Access Time: <20nsec

- Operation Temp.: -400C - 850C (can be extended to -550C - 1250C)

- Capacity: 256 Kbit (can be customized for 128Kbit - 2Mbit)

- Data Bus Width (Read): 32-bit (can be customized to 16-bit to 128-bit)

- System Interface: APB (can be customized AHB / AXI / OBI / QSPI)

- Endurance (Write cycles): 10K - 100K

- Data Retention: >=10years @125°C

Benefits

- Excellent endurance and retention even at high temperatures

- Ultra-low power consumption

- Tolerant to ionizing radiation and electromagnetic interference

- Inherently secure technology, deeply embedded between 2 metal layers

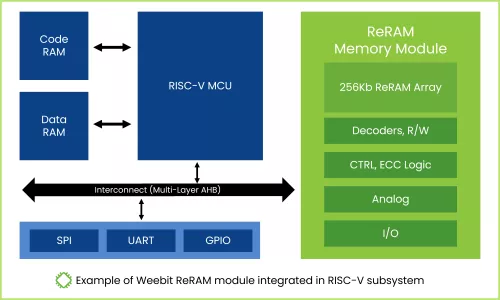

Block Diagram

Applications

- Analog, power management, mixed-signal designs

- IoT, industrial, automotive

- Radiation tolerant designs

- Heterogenous computing

- Data logging applications

Deliverables

- All standard IP deliverables including:

- Data sheet

- Integration guide

- Memory map

- Verilog model

- LEF

- CDL

- Timing constraints

Technical Specifications

Foundry, Node

ASIC, Foundry node SkyWater 130nm

Maturity

Silicon proven

Availability

Now

Related IPs

- Phase-frequency detector in CMOS logic

- NVM FTP Trim in TSMC (180nm, 152nm, 150nm, 130nm)

- NVM OTP in TSMC (180nm, 152nm, 130nm, 110nm, 90nm, 65nm, 55nm, 40nm, 28nm, 22nm, 16nm, 12nm, N7, N6, N5, N4P)

- 8-bit >100GSa/s Ultra-high-speed ADC in 16nm TSMC CMOS

- 8-bit <=51GSa/s Ultra-high-speed ADC in 16nm TSMC CMOS

- 8-bit <=120GSa/s Ultra-high-speed DAC in TSMC 16nm CMOS