The ADC has a maximum sampling rate of 7.6KS/s using an external clock of 100KHz frequency and an external convert signal that decides the sampling rate. It is a very low power ADC that takes only 70µW for its operation.

For flexibility of operation, the IP uses an internal reference buffer generating the reference voltage along with a high impedance interface to external reference voltage as well. This IP features good static performance that includes DNL <= 0.5LSB and INL <= 2LSB that results in having no missing codes.

The IP also features excellent dynamic performance having SNR >=56dB.

The IP has a design that can be easily ported across various foundries and processes upon request.

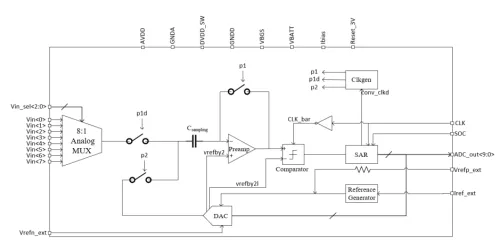

Low-Power 10-bit 4-channel SAR ADC

Overview

Key Features

- TSMC 65nm Low-Power Process

- 2.1-3.6V Battery Supply. 1.2V VDD Supply

- 10-bit Four-Channel SAR ADC

- Sampling Rate: 7.6KS/s

- Input Clock Frequency: 100KHz

- External Reference Current = 5µA

- Integrated Reference Buffer

- Outstanding Static Performance

- DNL = ±0.5LSB

- INL = 2LSB

- No Missing Codes

- Outstanding Dynamic Performance

- SNR = 56dB

- ENOB = 9 bits

- Low Power Dissipation

- 70µW (ADC + Ref. Buffer)

- Low Frequency Applications

Block Diagram

Technical Specifications

Foundry, Node

TSMC 65nm LP

TSMC

Pre-Silicon:

65nm

LP