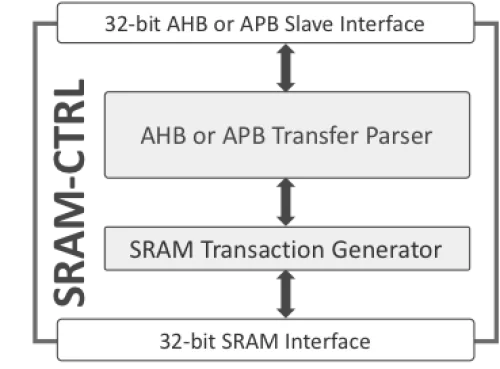

The SRAM-CTRL implements a SRAM Controller providing a standard AHB/APB interface to translate AHB/APB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

When the AHB interface is selected, the SRAM controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-to-back events: an AHB write directly followed by an AHB read. In this case, a single wait state is asserted.

When the APB interface is selected, the SRAM controller provides low latency APB access to the synchronous SRAM in all cases. APB write and read transfers are completed in two clock cycles.

The SRAM-CTRL core is rigorously verified, silicon-proven and available in RTL source or as a targeted FPGA netlist.

Internal Synchronous SRAM Controller Core

Overview

Key Features

- Interfaces

- - 32-bit host Interface compatible with either AMBATM AHB or APB-3 standards

- - Standard 32-bit, single-port synchronous SRAM interface

- Easy to Use and Integrate

- - Supports all types of AHB and APB transactions, including byte, half and word accesses

- - Zero wait state / low latency operation

- - No user programming required

- - User-settable AHB/APB interface and endianness

- - LINT-clean, scan-ready design

Block Diagram

Applications

- The SRAM-CTRL can be used in a variety of serial communication applications including a serial or modem computer interface, or a serial interface with modems and other devices.

Deliverables

- Synthesizable RTL or FPGA netlist

- Testbench & sample test cases

- Simulation & synthesis scripts

- Documentation

Technical Specifications

Maturity

Production Proven

Availability

Now