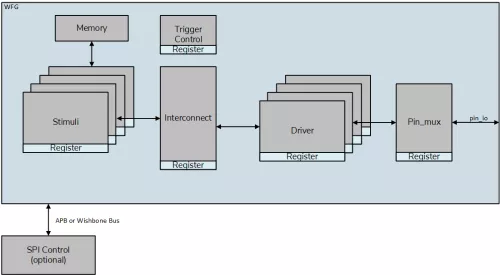

WFG represents a flexible and scalable waveform generation solution. Due to its layered approach of separating pin control, drive, and stimuli, WFG is easily adaptable to all types of waveforms and pattern generation.

For waveform generation many different protocol drivers are supported, like SPI, I2C, UART, and I2S. In addition, it is possible to generate and record typical parallel digital patterns, supporting all common tester formats (NRZ, RO, RZ,…).

There are several different ways of generating the required stimuli. Stimuli units for generating dedicated waveforms e.g., sine wave or triangular waveform, are available. A memory-based stimuli unit allows the creation of any type of waveform or pattern.

A central sampling rate and trigger unit allows controlling the different driver units in various ways. All blocks of the WFG can be configured via an APB or Wishbone bus interface. For systems without any internal bus a SPI based command decoder is also available.

Generic Waveform Generator

Overview

Key Features

- WFG supports many different drivers

- SPI, I2C, UART, I2S

- The number and type(s) of drivers can be configured

- WFG supports a digital pattern generation driver

- Supports all common tester formats (NRZ, RO, RZ,…)

- The bit width of the pattern generation driver can be configured

- WFG supports different stimuli units

- Sine wave, triangular waveform, and others

- The number of stimuli units can be configured

- WGF supports a generic memory-based stimuli unit

- Supports different operating modes like looping and endless mode

- The number, the bit width and depth of the memory-based stimuli unit can be configured

- WFG supports different configuration interfaces

- Standard bus interfaces APB and Wishbone

- Optional SPI based command decoder

Benefits

- Scalable approach

- Huge set of supported protocols

- Variable set of driver ans stimuli units possible

Block Diagram

Applications

- Any type of pattern of waveform generation. Either for implementation in an FPGA or an ASIC.

Deliverables

- Source code

- SystemVerilog RTL source code for the selected configuration

- Python (cocotb) based verification environment for sanity tests

- List of required integration tests

- Documentation

- Datasheet

- Integration guide

- Configuration register description

- Setup

- Sample FPGA project

- Support

- Technical integration support

- 12 month maintenance

Technical Specifications

Maturity

FPGA evaluation done

Availability

Now