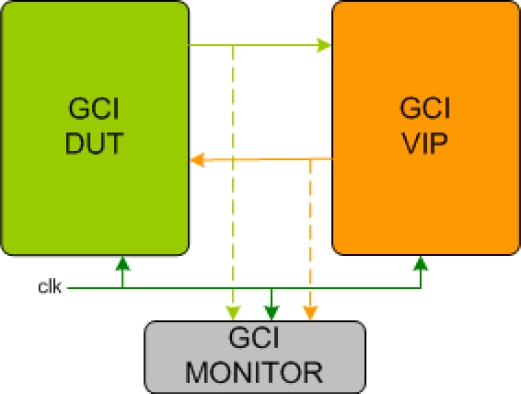

The GCI Verification IP is compliant with 1.3 specifications and verifies GCI interfaces of designs GCI Interface. It can work with SystemVerilog,Vera, SystemC, E and Verilog HDL environment. GCI Verification IP is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product.

GCI Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

GCI Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.