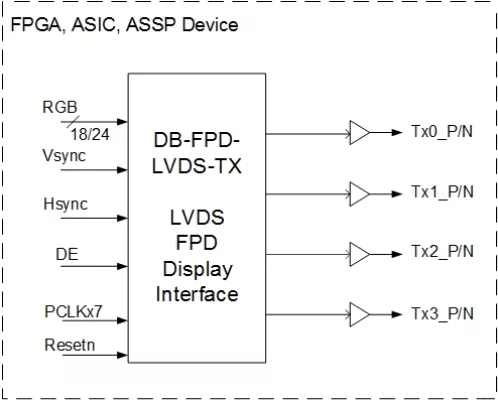

The Digital Blocks DB-FPD-LVDS-TX LVDS Display Interface IP Core interfaces parallel 18-bit/24-bit RGB Pixel Data with display timing VSYNC, HSYNC, Data Enable, and Pixel Clock to a FPD LVDS compliant display panel via 3 or 4 LVDS Differential Data Pairs and 1 LVDS Differential Clock Pair.

FPD LVDS Display Interface - 1 & 2 Port LVDS Panels

Overview

Key Features

- Supports 3 and 4 data and 1 clock LVDS differential pairs

- 18 / 24 bits-per-pixel (typically RGB or YCbCr)

- Example Range of Video Formats:

- HD 1280x720p

- Full HD 1920x1080p

- Cinema Full HD 2560x1080p

- UHD 4K x 2K 3840x2160p

- Dual Port LVDS Panel Support Provided

- Supports standardized FPD-Link Panels

- Compatible with commercial LVDS ICs:

- SN65LVDS*, SN75LVDS*,DS90CR*, DS90UR*, THC63LVD

- Supports 600 Mbps per data pair

- Differential Driver per data pair supplied by user from foundry technology library

- Fully-synchronous, synthesizable Verilog RTL core, with rising-edge clocking, no gated clocks, and no internal tri-states, for easy integration into FPGA or ASIC design flows.

- With DB9000 LCD Controller IP forms full Display System Solution for LVDS Interface panels

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

IBM, LSI. TMSC, UMC, Tower

Maturity

Successful in Company FPGA Kit Demo Reference Design, Customer Products

Availability

Immediately

Related IPs

- MIPI DSI to OpenLDI LVDS Display Interface Bridge

- OpenLDI LVDS to MIPI DSI Display Interface Bridge

- Open LVDS Display Interface (OpenLDI) Verification IP

- LCD Host LVDS Interface, Dual Pixel 20-112Mhz (SVGA/QXGA)

- Display LVDS single link/dual link Transmitter 1.12Gbps 8-Lane

- 1 Gbps DDR LVDS transmitter