eSPI Synthesizable Transactor provides a smart way to verify the eSPI component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's eSPI Synthesizable Transactor is fully compliant with standard eSPI base Specification rev.1.0 and provides the following features.

eSPI Synthesizable Transactor

Overview

Key Features

- Compliant with eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0

- Supports addendum 0.7

- Supports Master and Slave Modes

- Supports Single, Dual and Quad modes

- Supports TX and RX operation as per specs

- Supports below transaction phases

- Command Phase

- Turn-Around Phase

- Response Phase

- Supports baud rate selection

- Supports Slave triggered transaction

- Supports Interrupts and Alert

- Supports In-band reset

- Supports below multiple channels

- Peripheral channel

- Virtual Wires channel

- Flash Access channel

- Out Of Band message channel

- Various kind of Master and Slave errors detection and handling

- Supports CRC checking

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

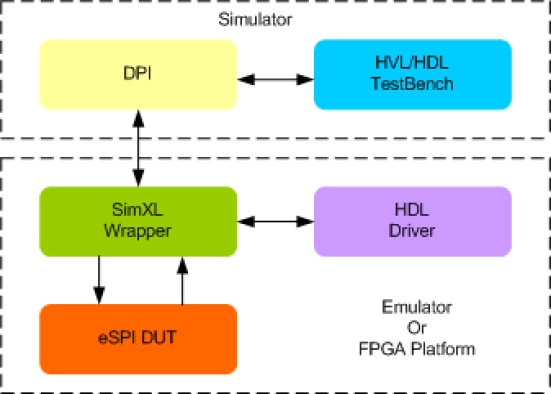

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the eSPI testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes