The CPRI IIP Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The CPRI IIP can be implemented in any technology. The CPRI IIP core supports the CPRI 7.0 Specification. It can also support a variety of host bus interfaces for easy adoption into any design architecture – AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

CPRI Controller IP

Overview

Key Features

- Compliant with CPRI Specification V4.2, V5.0, V6.0, V6.1 and V7.0.

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

- 614.4 MBPS

- 1228.8 MBPS

- 2457.6 MBPS

- 3072.0 MBPS

- 4915.2 MBPS

- 6144.0 MBPS

- 8110.08 MBPS

- 9830.4 MBPS

- 10137.6 MBPS

- 12165.12 MBPS

- 24330.24 MBPS

- Supports scrambler as in CPRI specification.

- Scrambler can be enabled or disabled.

- Supports 8B/10B line coding for bit rates upto 9830.4.

- Supports 64B/66B line coding without RS-FEC for 8110.08, 10137.6, 12165.12 and 24330.24 bit rates.

- Supports 64B/66B line coding with RS-FEC for 24330.24 bit rate

- RS-FEC with alignment marker and without scrambler support

- RS-FEC without alignment marker and with scrambler support

- RS-FEC without alignment marker and without scrambler support

- Performs CPRI Hyperframe Framing

- Performs interleaving of IQ data, sync, C&M data, and vendor specific information

- Provides an 8-bit, 16-bit, or 32-bit for IQ data

- Performs subchannel mapping:

- Supports a slow C&M channel based on a serial HDLC interface for following standard HDLC bit rates.

- 240 KBPS

- 480 KBPS

- 960 KBPS

- 1920 KBPS

- 2400 KBPS

- 3840 KBPS

- 4800 KBPS

- 7680 KBPS

- HDLC bit rate negotiated on higher layer

- Supports a fast C&M channel based on a serial Ethernet interface.

- Supports a slow C&M channel based on a serial HDLC interface for following standard HDLC bit rates.

- Performs synchronization and timing

- Supports the L1 Inband Protocol

- Provides a parallel interface for merging vendor specific data into the CPRI frame

- Provides a start-up sequence state machine in hardware for both REC and RE nodes which performs:

- L1 Synchronization

- Protocol setup

- C&M Plane setup

- Supports Link Maintenance

- LOS detection

- LOF detection

- RAI indication

- SDI indication

Benefits

- Single site license option is provided to companies designing in a single site.

- Multi sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

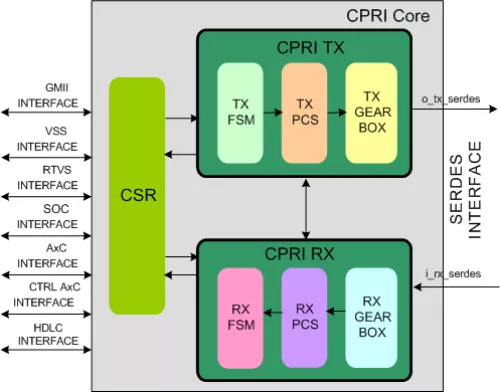

Block Diagram

Deliverables

- The CPRI Controller interface is available in Source and netlist products.

- The Source product is delivered in plain text verilog or VHDL or SystemC source code

- Integration testbench and tests

- Scripts for simulation and synthesis with support for common EDA tools

- Documentation contains User s Guide and Release notes.