Flexis™ family controllers from Freescale Semiconductor, the world’s leading provider of 32-bit embedded controllers, provide the link between 8-bit ease-of-use and 32-bit performance. Freescale’s pair of pin-compatible controllers—the 8-bit S08QE128 and 32-bit V1 ColdFire based MCF51QE128—are the industry’s first fully compatible 8-bit and 32-bit architectures, sharing a common set of peripherals and development tools.

Fully compatible with the V2, V3, and V4 ColdFire architectures as well as the 8-bit S08 architecture, V1 ColdFire provides an entry point to the popular 32-bit ColdFire processor continuum.

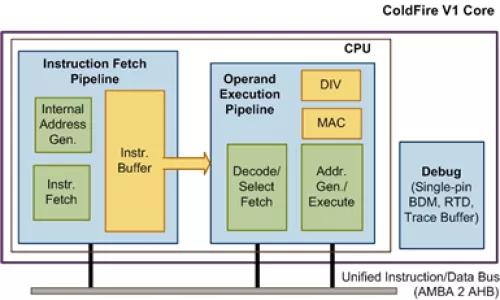

The V1 ColdFire Core offers a low-cost entry point to the ColdFire roadmap. A simplified version of the V2 ColdFire architecture, the V1 ColdFire Core is a low-power, low-gate-count implementation with a single-wire debug interface. Integration cost is minimized through simple interfaces to on-chip logic: unified instruction/data bus, interrupt, clock, and reset.

Debug support including real-time trace (RTT) and real-time debug (RTD) is through a single-wire background debug module (BDM) interface. The debug unit includes an embedded trace buffer with data compression for efficient storage and transfer of trace data.

A separate debug clock enables shut-down of debug logic when not in use.

The V1 ColdFire instruction set includes special MAC/DIV instructions executed in dedicated MAC/DIV hardware, features improved handling of byte (8-bit) and word (16-bit) operands, and offers upward compatibility with other ColdFire cores such as the V2.

ColdFire V1 Processor

Overview

Key Features

- 32-bit processor core with 24-bit address bus

- AMBA 2 AHB unified instruction/data bus

- Single-wire debug interface

- Variable-length RISC architecture with 16, 32, and 48-bit instructions

- Independent, decoupled instruction and execution pipelines

- 2-stage Instruction Fetch Pipeline (IFP)

- 2-stage Operand Execution Pipeline (OEP)

- Static branch prediction to minimize change-of-flow execution time

- Execute engines include ALU, barrel shifter, and optional MAC and DIV units

- ColdFire Instruction Set Architecture Rev. C (ISA_C)

- Standard ColdFire programming model with 16 general-purpose, 32-bit registers

- Simplified supervisor programming model supporting a supervisor stack pointer, vector base register, and CPU configuration register

- Programmable response upon detection of certain illegal opcodes and illegal addresses (processor exception or system reset)

- Optional debug support including trace and real-time debug (RTD) through a single-wire background debug module (BDM) interface

- Optional Multiply-Accumulate (MAC) Unit & Divider (DIV) Unit

Block Diagram

Video

Putting the ColdFire Family to Work for You

Deliverables

- The ColdFire V1 CORE is available in Verilog source RTL

- The deliverables include:

- Verilog source code

- Integration Testbench and Test-suite

- Comprehensive Documentation

- Scripts for simulation and synthesis with support for common EDA tools

Technical Specifications

Maturity

Silicon Proven

Availability

now