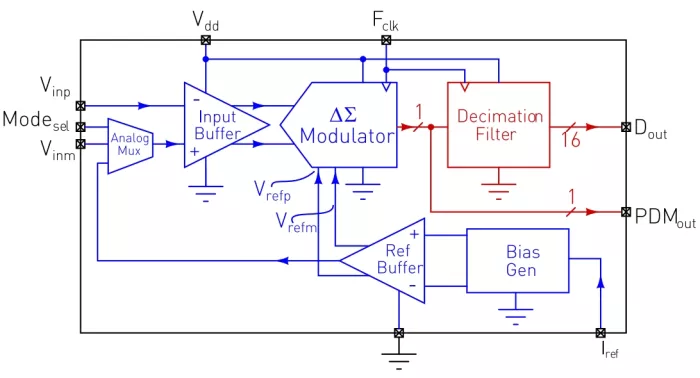

A solution including an input buffer with programmable gain, followed by a Delta Sigma Modulator (DSM) and a Decimation filter is provided. Additionally, the voltage reference buffers, the current generation and DC bias generators are integrated within this solution.

The input impedance is resistive and hence can be easily driven by the preceding stage which may be another analog block or even directly a sensor. Furthermore, the input buffer can be configured to accept either

single-ended or differential voltage inputs making it more convenient to interface with single-ended output blocks/sensors.

The DSM outputs an oversampled single bit stream which is input to an internal decimation filter to filter off the high-frequency noise. The decimation

factor is configurable and hence the output data rate can be increased or decreased by trading off with performance as and when required. Additionally, aprovision is made to output both the 16-bit word from

the decimation filter and the oversampled 1-bit stream from the DSM, as and when demanded.

32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB

Overview

Key Features

- 13/11.5/10 bit ENOB over 8/16/32 kHz signal bandwidth respectively

- Supply voltage of 1.8 V for both analog and digital

- Low power consumption and small silicon footprint

- Built-in programmable gain input buffer with resistive input impedance

- Built-in voltage reference buffer for the ADC

- Widely configurable clock frequencies from 512 kHz to 2.048 MHz

- Configurable decimation factors of 32, 64 and 128

- Configurable to accept single-ended or differential inputs

- Digital output in 1 bit PDM format at oversampled rate or 16 bit decimated output at Nyquist rate

- Built-in dithering feature to prevent idle tones & limit-cycles

Block Diagram

Applications

- Voice-activated systems

- Audio capture, recording and digitization

- Filterless PDM output microphones

- Bio-medical applications like ECG, EEG and EMG readouts

- Multichannel digitization and digital readout

Technical Specifications

Foundry, Node

180nm

Maturity

Silicon proven

Related IPs

- Up to 50% main memory bandwidth acceleration

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- Output Buffer for up to 12Gb/s

- 16-bit 2-channel 25 kHz bandwidth delta-sigma stereo, audio DAC

- 24-bit 320kHz Bandwidth ADC IP

- 12-bit 1-channel up to 1.25MSPS SAR ADC