DLL IP for TSMC

Welcome to the ultimate DLL IP for TSMC hub! Explore our vast directory of DLL IP for TSMC

All offers in

DLL IP

for TSMC

Filter

Compare

405

DLL IP

for TSMC

from 6 vendors

(1

-

10)

-

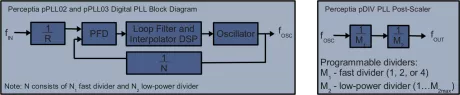

High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- Fractional-N digital PLL architecture, using an LC-tank oscillator

-

Low Voltage, Low Power Fractional-N PLLs

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

General Purpose Fractional-N PLLs

- Low power, suitable for logic clocking applications

- Extremely small die area, using a ring oscillator

- Twelve bits fractional resolution

-

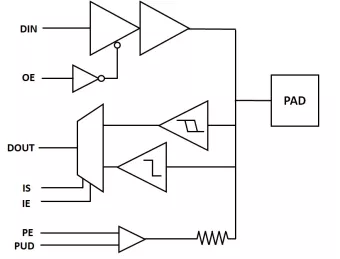

A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell

- GPIO:

- I2C / SMBUS Open-Drain I/O:

- LVDS

- ANALOG

-

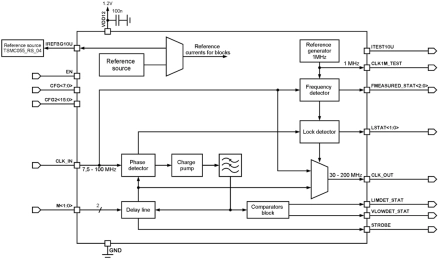

30-200 MHz DLL-based frequency multiplier

- TSMC CMOS 55 nm

- 30 – 200 MHz output frequency

- 7.5 – 100 MHz reference frequency

- Multiplication factor 1, 2, 3 or 4

- Glitch-free mode switching

-

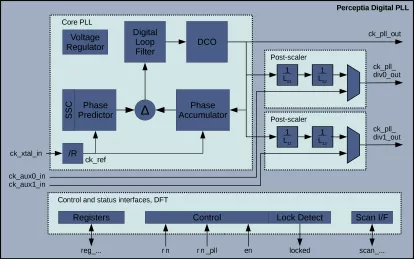

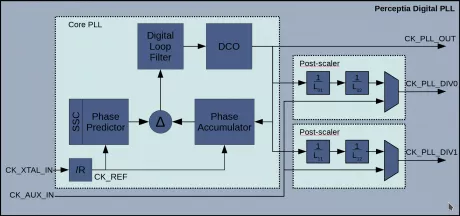

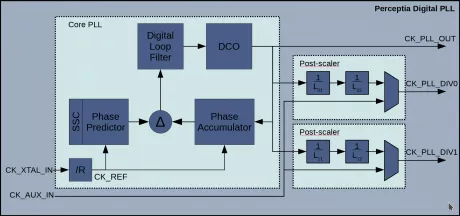

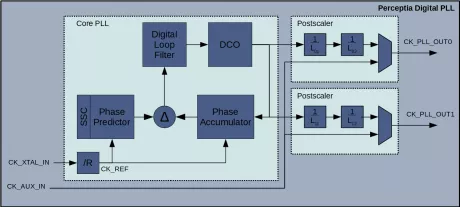

4-GHz Jitter-optimized low-power digital PLL

- - Jitter below 10-ps

- - Super small: 90 x 90 microns!

- - Very low power: 15-mW

- - Broad frequency range: 4-GHz

-

Minimum-area low-power clocking PLL (1st gen)

- - Super small: 80 x 80 microns!

- - Very low power: 12-mW

- - Broad frequency range: 2-GHz

- - Fast lock

-

TSMC CLN7FFLVT 7nm Multi Phase DLL - 1200MHz-6000MHz

- Designed for high-speed interface applications.

- Generates precise multi-phase clocks directly from the reference clock.

- Delivers optimal jitter performance over a wide frequency range.

-

TSMC CLN7FFLVT 7nm DDR DLL - 360MHz-1800MHz

- Designed for high-speed DDR style interface applications.

- Generates precise delays that can be programmed from 0 to 360 degrees of the reference period.

- Delays multiple periodic or aperiodic signals independent of voltage and temperature.

- Delivers optimal jitter performance over a wide frequency range.

-

TSMC CLN7FF 7nm DDR DLL - 250MHz-1250MHz

- Designed for high-speed DDR style interface applications.

- Generates precise delays that can be programmed from 0 to 360 degrees of the reference period.

- Delays multiple periodic or aperiodic signals independent of voltage and temperature.

- Delivers optimal jitter performance over a wide frequency range.