The DisplayPort Forward Error Correction (FEC) Receiver IP Core implements Reed-Solomon FEC and symbol interleaving as specified by the VESA DisplayPort 2.0 specification. Forward Error Correction is required to ensure low bit error rate at UHBR link rates and glitch-free Display Stream Compression (DSC) bitstream transport.

VESA DisplayPort 2.0 FEC RX

Overview

Key Features

- VESA DisplayPort 2.0 compliant

- Reed Solomon RS (198,194) FEC, 8-bit symbols

- Multiple symbols per clock

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode

- requires 2 FEC IP core instances)

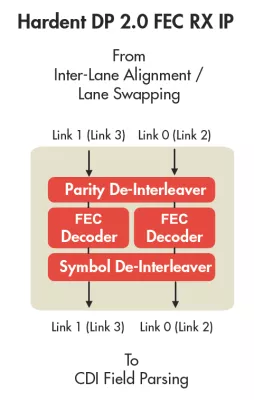

Block Diagram

Applications

- UHD monitors

- DisplayPort 2.0 hubs & accessories

- USB Type-C hubs & accessories

- UHD TVs

Deliverables

- Encrypted RTL source code IP core

- Functional and structural coverage reports

- Comprehensive integration guide

- Technical support and maintenance updates

Technical Specifications

Related IPs

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Receiver

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- ASIL-B Ready ISO 26262 Certified VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

- GPON FEC 2.5 Gbps