VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

Key Features

- Complete DisplayPort™ 1.4 Receiver solution with support for VESA Display Stream Compression (DSC)

- Fully compliant with the DisplayPort 1.4a Standard

- Including the DSC slices per line requirements

- Supports up to 4 lanes at HBR3 rate (8.1 Gbits/sec)

- Configurable maximum display resolution up to 8K (FUHD) 60fps in RGB 444

- All color spaces supported by DSC v1.2a and component bit depth up to 12 bits

- Support for Xilinx® UltraScale™ and UltraScale+™ devices

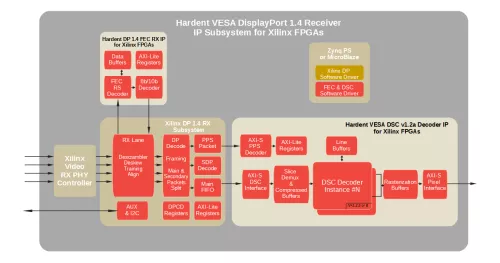

Block Diagram

Applications

- 4K / 8K Monitors

- Digital Signage

- Video Converters

- Projectors

- Multiviewers

Deliverables

- Xilinx Video PHY Controller & DisplayPort 1.4 RX Subsystem IP

- Hardent VESA DisplayPort 1.4 Forward Error Corrector (FEC) Receiver IP for Xilinx FPGAs

- Hardent VESA Display Stream Compression (DSC) 1.2a Decoder IP for Xilinx FPGAs

- Reference design with Vivado® Design Suite & SDK project files

- Documentation for each Hardent IP core

- Comprehensive integration guide

- Software drivers and user application example

- Technical support from Hardent included

Technical Specifications

TSMC

Pre-Silicon:

40nm

LP

Related IPs

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Receiver

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DSC 1.2b Encoder for Xilinx FPGAs

- VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 2.0 FEC RX