VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

The DisplayPort Forward Error Correction (FEC) Transmitter IP core implements Reed-Solomon FEC and symbol interleaving as specifi…

Overview

The DisplayPort Forward Error Correction (FEC) Transmitter IP core implements Reed-Solomon FEC and symbol interleaving as specified by the VESA DisplayPort 1.4 specification. Forward Error Correction is required to ensure glitch-free Display Stream Compression (DSC) bitstream transport.

Solution for GPUs, UHD Set-top Boxes, Desktop and Laptop PCs, USB-C/DisplayPort Accessories

Key features

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

- Single unified APB interface supports 4-lane mode (Rx)

- Performance monitoring and statistics counters (Rx)

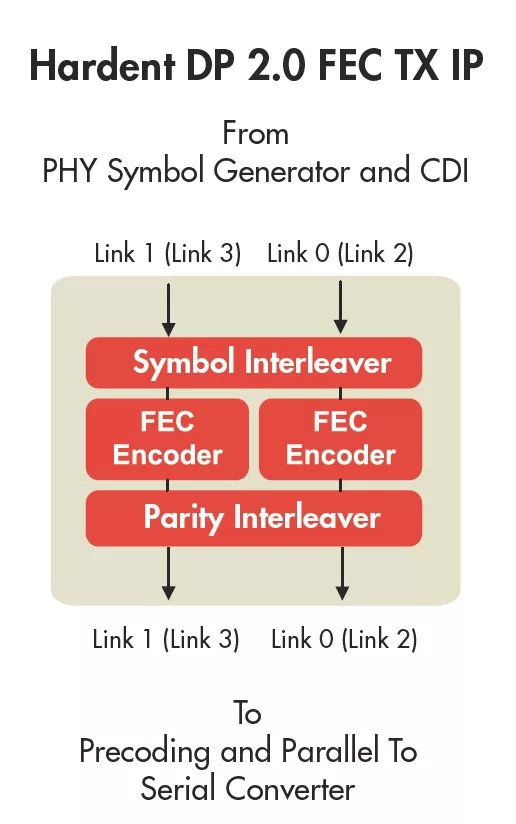

Block Diagram

Applications

- GPUs

- Desktops & laptops

- UHD TVs and set-top boxes

- USB Type-C & DisplayPort products

- Tablets & mobiles

What’s Included?

- Encrypted RTL source code IP core

- Functional and structural coverage reports

- Comprehensive integration guide

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter?

VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter is a Channel Coding IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.