The PCIe GEN6 PHY IP achieves data rates up to 64GT/s per lane with PAM4 signaling thereby delivering reliable performance for high-speed data transfer. It supports advanced applications, including AI/ML, High-Performance Computing, and next-generation storage solutions.

PCIe GEN6 PHY IP

Overview

Key Features

- Supports PRBS (Pseudo Random Binary Sequence) testing including loopback modes

- Supports different power states as defined in PCIe PHY specification

- Supports 100MHz common reference clock between RC and EP

- Supports the PCIe Gen6 compliance/modified compliance (PCIe base 6.2 sections 4.2.14-15)

- Supports 52UI jitter measurement (PCIe base 6.2 section 4.2.16)

- Supports High swing toggle (PCIe base 6.2 section 4.2.17)

Benefits

- Designed for next-generation PCIe systems, the PCIe GEN6 PHY IP supports data rates up to 64GT/s per lane with advanced PAM4 signaling.

- It ensures efficient data handling for demanding applications such as AI, ML, high-performance computing, and modern storage technologies.

- With scalable throughput and a focus on reliability, this PHY IP simplifies integration into high-speed, data-intensive use cases.

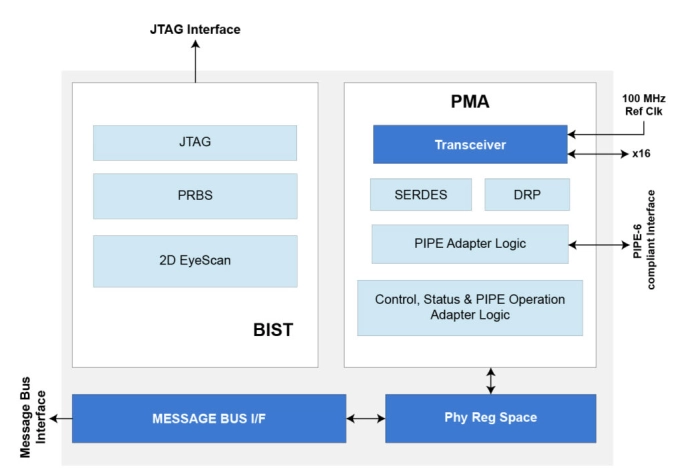

Block Diagram