The DB9200AXI4 2D Graphics Engine Verilog IP Core targets low VLSI footprint, high-performance hardware accelerated graphics applications.

The DB9200AXI4 2D Graphics Engine renders graphics frames by generating bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations; generates characters from compressed bitmaps using its FONT Bitmap Color Expansion feature; performs alpha blend operations of bitmaps with its Alpha Blend unit; draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham line drawing Unit.

The DB9200AXI4 2D Graphics Engine provides options for higher graphics performance as a Graphics Processing Unit (GPU) with its Display List Processing Unit addition; Parallel Pixel Processing capabilities; and Memory Interface Units that unlock the graphics memory bottleneck.

2D Graphics Hardware Accelerator (AXI4 Bus)

Overview

Key Features

- Bit Block Transfer – 3 Independent Memory Sources of data:

- On-Screen & Off-Screen Data Block (SRC)

- Off-Screen Fixed Pattern Data Block (PTN)

- On-Screen visible Data Block (DST)

- 2D Raster Operations (ROP) performed on Block Transfers:

- 256 Raster Operations

- ROP0, ROP1, ROP2, & ROP3 operations

- Includes industries most popular 16 ROPs

- BitBLT Draw Features:

- Pixels, Horizontal & Vertical Lines

- Overlapping & Non-Overlapping Block Transfers

- Solid Color Block Fills

- FONT Monochrome Bitmap to Color Expansion, either Transparent or Opaque

- Rotation Block Transfers: 0, 90, 180, 270 degrees

- Block Stretch on X & Y Axis

- Alpha Blending

- Sprite Moves

- 2D Graphics Rendering Engine:

- Pixel Drawing

- Line (Vector) Drawing – any direction

- Polygon Rendering

- Filled Polygon

- Command FIFO or Link-List Display Processing Unit

- Frame Buffer & Display Features Supported

- Display Resolutions 4K x 4K

- 8, 16 , 24, & 32 bits-per-pixel color depths

- Interrupt Controller with 3 sources of internal interrupts with masking control

- Reference Software Driver Included

- On-Chip Interconnect Compliance - AXI, AXI4, AHB, Avalon

- Compatible with Digital Blocks DB9000 Family of TFT LCD Controller IP Cores and Reference Designs

- Fully-synchronous, synthesizable Verilog RTL core

Benefits

- The DB9200 family of 2D Graphics Hardware Accelerator IP Cores provides a higher graphics performance than a Host, while offering higher software productivity.

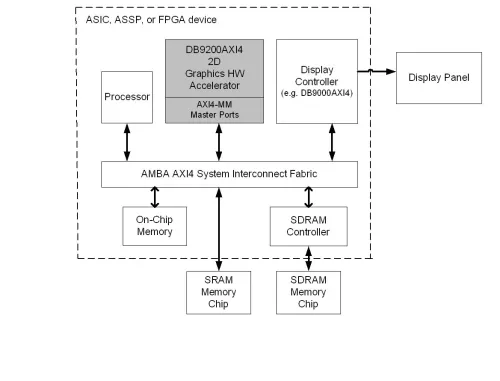

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

IBM, TMSC, UMC, Tower, Fujitsu, GlobalFoundries, STMicroelectronics, SMIC, Common Platform, Chartered, OKI

Maturity

Successful in Company FPGA Kit Demo Reference Design, Customer Products

Availability

Immediately

Related IPs

- BitBLT Graphics Hardware Accelerator (AXI4 Bus)

- 2D Vector Graphics Accelerator / GPU (Graphics Processing Unit)

- BitBLT Graphics Hardware Accelerator (AXI Bus)

- BitBLT Graphics Hardware Accelerator (AHB Bus)

- 2D/3D Vector Graphics Accelerator / GPU (Graphics Processing Unit)

- High-performance 2D (sprite graphics) GPU IP combining high pixel processing capacity and minimum gate count.