This JPEG compression IP core supports the Baseline Sequential DCT and the Extended Sequential DCT modes of the ISO/IEC 10918-1 standard. It implements a scalable, ultra-high-performance, ASIC or FPGA, hardware JPEG encoder that can compress high pixel rate video using significantly fewer silicon resources and less power than encoders for video compression standards such as HEVC/H,265, DSC, AVC/H.264, or JPEG200.

The JPEG-EX-F Encoder produces compressed JPEG images and the video payload for Motion-JPEG container formats. It accepts images with up to 12-bit color samples and up to four color components, in all widely-used color subsampling formats.

Depending on its configuration, the encoder processes from two to 32 color samples per clock cycle, enabling it to compress UHD (4K/8K) video and/or very high frame video.

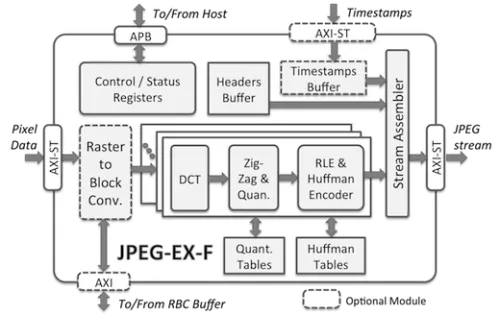

Once programmed, the easy-to-use encoder requires no assistance from a host processor to compress an arbitrary number of frames. SoC integration is straightforward thanks to standardized AMBA® interfaces: AXI Streaming for pixel and compressed data, and a 32-bit APB slave interface for registers access. Users can optionally insert timestamps or other metadata in the compressed stream using a dedicated AXI Streaming interface.

Customers with a short time to market priority can use CAST’s IP Integration Services to receive complete JPEG subsystems. These integrate the JPEG encoder with video interface controllers, Hardware UDPIP or Transport Stream networking stacks, or other IP cores available from CAST.

The core is designed with industry best practices, and its reliability and low risk have been proven through both rigorous verification and customer production. Its deliverables include a complete verification environment and a bit-accurate software model.

Ultra-Fast Baseline and Extended JPEG Encoder Core

Overview

Key Features

- Scalable, ultra-high performance 4K/8k capable JPEG Encoder

- Requires significantly lower power and fewer silicon resources than any equally fast hardware video encoder for HEVC/H,265, AVC/H.264, DSC, or JPEG2000.

- Consumes much less power than any equivalent software, or software-hardware encoder.

- Standards Support

- ISO/IEC 10918-1 Baseline and Extended (Sequential DCT) modes

- Single-frame JPEG images and Motion JPEG payloads

- 8-bit and 12-bit per color samples

- Up to four color components; any image size up to 64k x 64k

- All scan configurations and all JPEG formats APP, COM, and restart markers

- Programmable Huffman Tables Quantization tables

- Rate Control Options

- Image: Limits the size of each individual frame

- Video: Regulates bit rate over a number of input frames

- Interfaces

- AXI Streaming pixel and compressed stream interfaces

- APB Control/Status interface

- Performance

- Synthesis-time configurable scalable throughput

- Up to 32 samples per clock cycle

- Supports UHD (4k/8K) video and/or ultra-high frame rates

- Ease of Integration

- Automatic program-once/encode-many operation

- Simple, dedicated timestamps interface

- Bit-accurate software model generates test vectors, expected results, and core programming values

- Optional Raster-to-Block Conversion with AXI or standard memory interface to the lines buffer

Block Diagram

Applications

- The JPEG-EX-F core is suitable for systems supporting ultra-high frame resolutions and/or frame rates, such as:

- Corporate, airborne, and other security or surveillance systems.

- Machine vision and video link decoders or terminals for industrial, or defense systems.

- Medical imaging systems.

Deliverables

- Verilog RTL source code

- Sophisticated self-checking Testbench

- Software (C++) Bit-Accurate Model

- Sample simulation and synthesis scripts

- Comprehensive user documentation

Technical Specifications

Maturity

Production Proven

Availability

Now

Related IPs

- Ultra-Fast Baseline and Extended JPEG Decoder Core

- 10/12-bit Extended & 8-bit Baseline JPEG Encoder with optional Constant Bitrate Motion JPEG Video Rate Control

- 10/12-bit Extended and 8-bit Baseline JPEG Image & Video Decoder

- Baseline and Extended JPEG Encoder Core

- Baseline and Extended JPEG Decoder Core

- Baseline and Extended JPEG Decoder Core