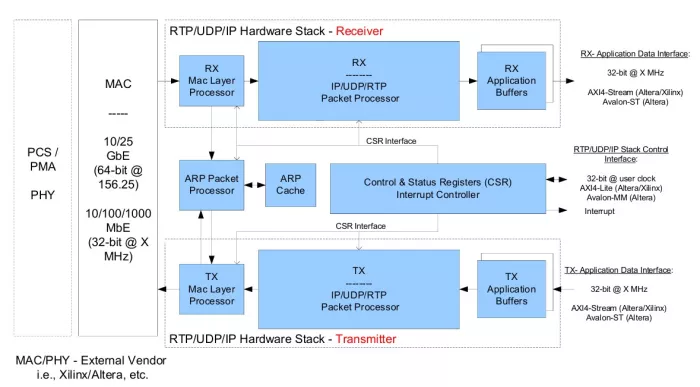

The DB-RTP-UDP-IP-NAL Intellectual Property Core is an RTP/UDP/IP Protocol Hardware Stack with the following protocol processing units:

- RTP Packet Processor

- UDP Packet Processor

- IP Packet Processor

- MAC Frame Layer Processor

For RX (i.e., receiving packets from the network), there is optional packet reordering to absorb network jitter.

For both TX/RX, multiple NAL video streams supported. The DB-RTP-UDP-IP-NAL targets H.264 NAL Streams. See DB-RTP-UDP-IP-AV for raw, uncompressed RGB/YUV video streams.